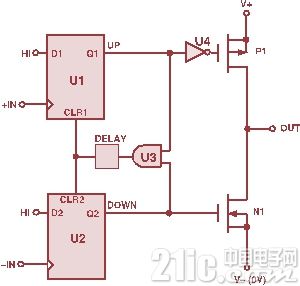

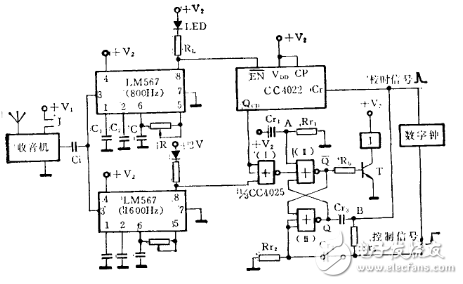

- 模拟锁相环电路锁定检测问题解答 1.PLL锁定有那些检测方法,它们特点是什么? 一种是最为简单的数字检测,它利用输入参考的分频信号与VCO反馈的分频信号,在PFD里鉴相的结果,通过连续结果时钟周期检测到鉴相的脉宽小于某值,作为锁定的有效判决规则。这种检测方式,判决方式简单,判断的结果只有锁定和非锁定两种情况。 另一种方式是模拟锁定检测,也称为N沟道漏级开路检测,它的实现原则是通过对于PFD输出的超前和滞后脉冲做XOR操作,直接将得出的结果输出。由于XOR的结果有是一串高低的脉冲,所以需要外部电路

- 关键字:

锁相环 PLL

- 摘要:相位锁定检测电路是锁相环环路的关键电路,其性能的优劣直接影响了整个系统的工作。本文描述了相位锁定检测电路的工作原理,根据项目实际提出一种相位锁定检测方案,按照全定制设计流程采用SMIC0.18mu;m CMO

- 关键字:

相位锁定检测 CMOS电路 锁相环 收发器

- 摘要:针对微机保护中采用传统的采样方法,采样频率难以自动跟踪被测量的频率变化而发生变化,必然会导致FFT运算产生误差。本文采用锁相环同步采样技术实现对微机保护装置中交流电压、电流信号的频率和相位进行锁定,

- 关键字:

同步采样 锁相环 AD7656 微机保护

- 十几年前,频率控制行业推出了基于锁相环(PLL)的振荡器,这是一项开拓性创新技术,采用了传统晶体振荡器(XO)所没有的多项特性。凭借内部时钟合成器IC技术,基于PLL的XO可编程来支持更宽广的频率范围。这一突破消除了

- 关键字:

锁相环 PLL 振荡器 抖动 相位噪声

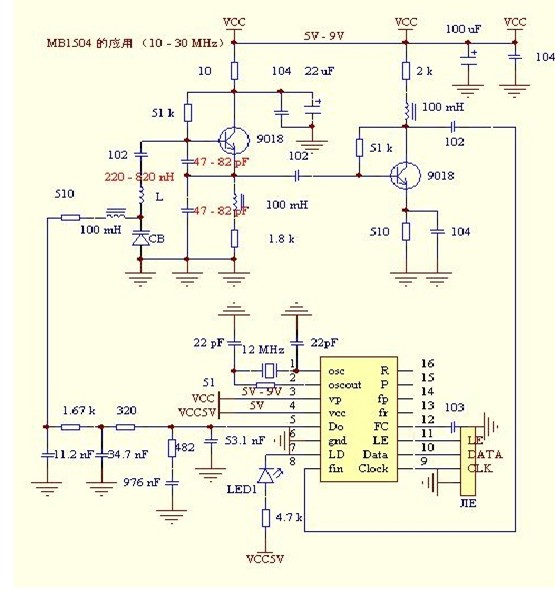

- 摘要:本设计采用Hittite公司生产的频率合成器芯片HMC703LP4E为核心,通过上位机经FPGA输入控制信息来产生雷达系统使用的步进频率信号。该频率源具有输出信号频带宽、变频时间短、信号稳定的特点,在雷达系统设计中已

- 关键字:

锁相环 HMC703LP4E 变频时间 步进频信号

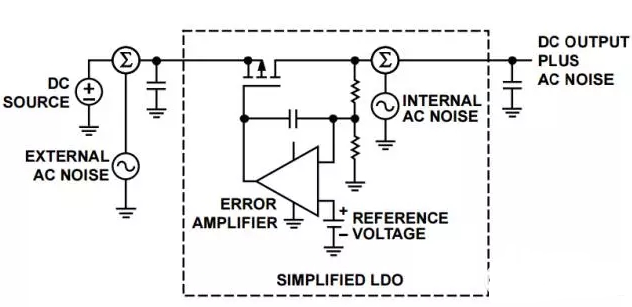

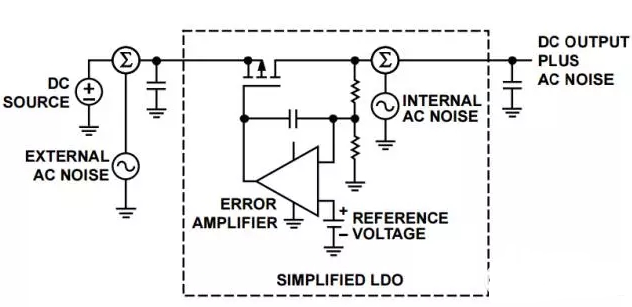

- 为了成功设计一个鲁棒的系统,了解噪声源至关重要。就低压差(LDO)调节器而言或者说任何电路,噪声源都可以分为两大类:内部噪声和外部噪声。

噪声重要与否,取决于它对目标电路工作的影响程度。

例如,一个开关电源在3 MHz时具有显著的输出电压纹波,如果它为之供电的电路仅有几Hz的带宽,如温度传感器等,则该纹波可能不会产生任何影响。但是,如果该开关电源为RF锁相环(PLL)供电,结果可能大不相同。

为了成功设计一个鲁棒的系统,了解噪声源至关重要。就低压差(LDO)调节器而言或者说任何电路,

- 关键字:

LDO 锁相环

- 在尝试将锁相环(PLL)锁定时,你是否碰到过麻烦?草率的判断会延长调试过程,调试过程变得更加单调乏味。根据以下验证通行与建立锁定的程序,调试过程可以变得非常简单。

第1步:验证通信

第一步是验证PLL响应编程的能力。如果PLL没有锁定,无法读回,则尝试发送需要最小量硬件命令工作的软件命令。一种方法是通过软件(而非引脚)调节PLL的通电断电寻找引脚的可预测电流变化或偏置电压电平变化。许多PLL在其输入(OSCin)引脚的电平在通电时为Vcc/2,在断电时为0V。

如果PLL集成了压控振

- 关键字:

锁相环 PLL

- 滤波器一些问题的补充:

关于滤波器的技术指标,包含裕度、截止频率、带内波动、带内驻波比、带内相位线性度

巴特沃兹、切比雪夫、贝塞尔滤波器电路分析、传递函数。包含低通、高通、带通。

技术指标补充

裕度:相位裕度是锁相环开环传递函数在伯德图(由两张图组成:一张是对数幅频特性,它的纵坐标为20lg|G(jw)|,单位是分贝,用符号dB表示。另一张是对数相频特性,纵坐标是角度。)上形成的性能参数,是用于考核锁相环稳定性的依据。其定义与计算方法是:分别画出锁相环开环传递函数的幅频与相频曲

- 关键字:

滤波器 锁相环

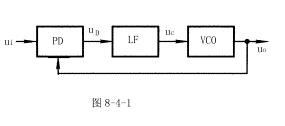

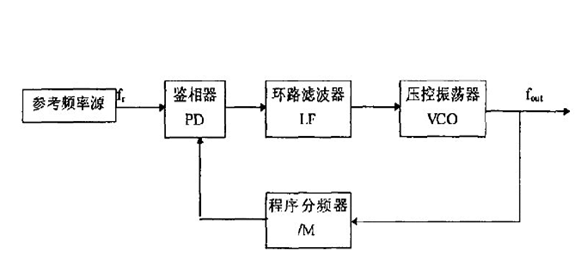

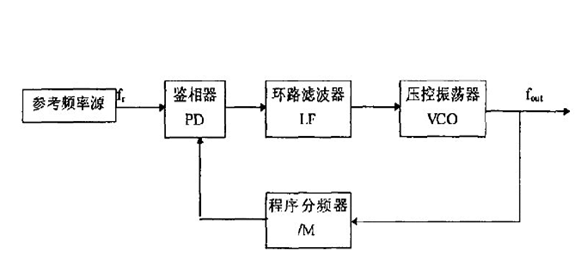

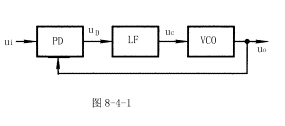

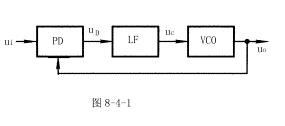

- 1.锁相环的基本组成

许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由

- 关键字:

锁相环 PLL

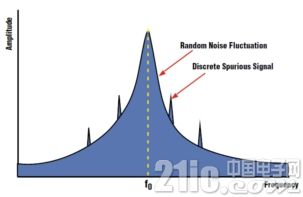

- 本系列第一部分介绍了锁相环(PLL),说明了其基本架构和工作原理。 另外举例说明了PLL在通信系统中的用途。 在第二部分中,我们详细考察了相位噪声、参考杂散、输出漏电流等关键性能规格,还考虑了它们对系统性能的影响。 在本部分中,我们将考察PLL频率合成器的主要构建模块。 我们还将比较整数N和小数N架构。 最后将总结市场上现有的VCO,同时列出ADI的现有频率合成器系列。 PLL频率合成器基本构建模块 PLL频率合成器可以从多个基本构建模块的角度来考

- 关键字:

高频接收器 锁相环

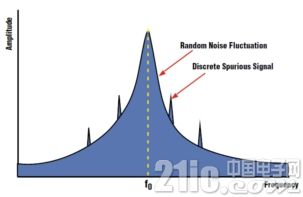

- 本系列文章的第一部分介绍了关于锁相环(PLL)的基本概念,说明了PLL架构和工作原理,同时以一个例子说明了PLL在通信系统中的用途。 在第二部分中,我们将侧重于详细考察与PLL相关的两个关键技术规格:相位噪声和参考杂散。导致相位噪声和参考杂散的原因是什么,如何将其影响降至最低?讨论将涉及测量技术以及这些误差对系统性能的影响。我们还将考虑输出漏电流,举例说明其在开环调制方案中的重要意义。 振荡器系统中的噪声 在任何振荡器设计中,频率稳定性都至关重要。我们需要考虑长期和短期稳定性。长期频率稳定性是关

- 关键字:

发射器 锁相环

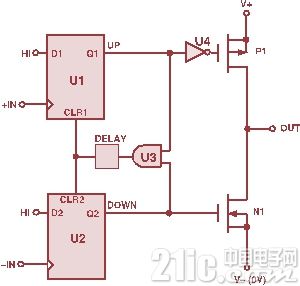

- 本文介绍了浅谈锁相环电路的模拟锁定检测问题

1.PLL锁定有那些检测方法,它们特点是什么?

一种是最为简单的数字检测,它利用输入参考的分频信号与VCO反馈的分频信号,在PFD里鉴相的结果,通过连续结果时钟周期检测到鉴相的脉宽小于某值,作为锁定的有效判决规则。这种检测方式,判决方式简单,判断的结果只有锁定和非锁定两种情况。

另一种方式是模拟锁定检测,也称为N沟道漏级开路检测,它的实现原则是通过对于PFD输出的超前和滞后脉冲做XOR操作,直接将得出的结果输出。由于XOR的结果有是一串高低

- 关键字:

锁相环

- 本文给大家介绍了锁相环的组成和工作原理。

1.锁相环的基本组成

许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出

- 关键字:

锁相环

锁相环介绍

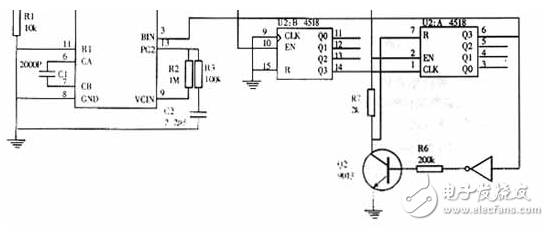

能使受控振荡器的频率和相位均与输入信号保持确定关系的闭环电子电路。锁相环的基本结构如图1,其中鉴相器用来鉴别输入信号ui与输出信号u0之间的相位差,并输出误差电压ud。ud中的噪声和干扰成分被低通性质的环路滤波器滤除,形成压控振荡器(VCO)的控制电压uC。uC作用于压控振荡器的结果是把它的输出振荡频率f0拉向环路输入信号频率fi,当二者相等时,环路被锁定,称为入锁。维持锁定的直流控制电压由鉴相器 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473