- 基于0.13微米CMOS工艺下平台式FPGA中可重构RAM模块的一种设计方法,1. 引言

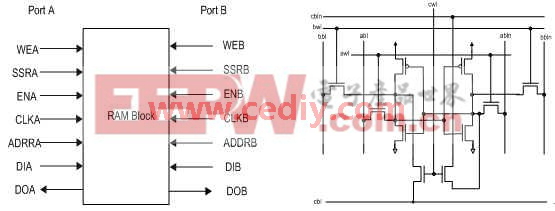

对于需要大的片上存储器的各种不同的应用,FPGA 需要提供可重构且可串联的存储器阵列。通过不同的配置选择,嵌入式存储器阵列可以被合并从而达到位宽或字深的扩展并且可以作为单端口,双端口

- 关键字:

RAM 重构 模块 设计 方法 FPGA 平台 0.13 微米 CMOS 工艺

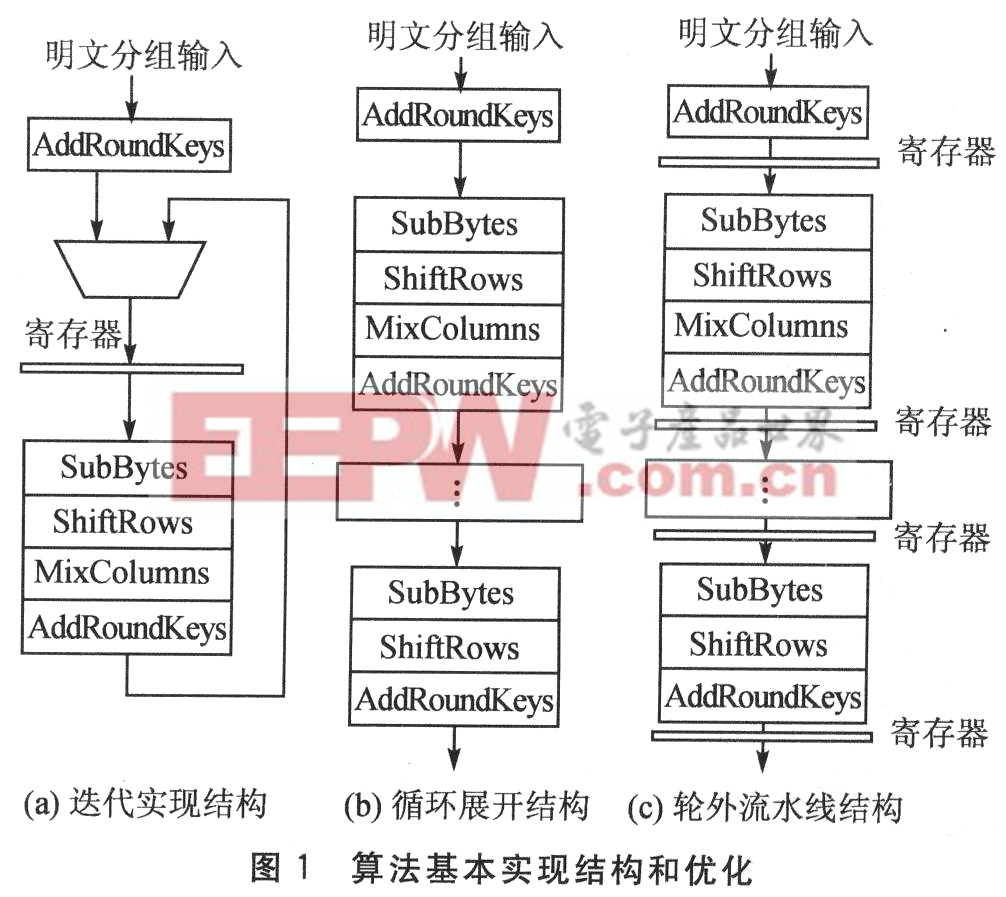

- 摘要 AES-Rijndael算法是美国取代DES的新一代分组加密算法标准,也是事实上的国际标准。本文在可重构平台上针对 128位密钥长度AES算法的流水线性能优化技术进行了研究,通过对基本运算优化、循环展开、轮内流水线、轮

- 关键字:

性能 优化 流水线 算法 平台 AES 重构

重构介绍

重构 重构的定义

重构(名词):对软件内部结构的一种调整,目的是在不改变"软件之可察行为"前提下,提高其可理解性,降低其修改成本.

重构(动词):使用一系列重构准则(手法),在不改变"软件之可察行为"前提下,调整其结构.

两种定义都强调是在不改变"软件的外部行为"前提下,不改变"软件之可察行为"就是说让修改不影响外部使用程序(程序员),在个外部来看,程序的行为和结果没有任何的变 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473