- 锁相环控制及初始化简析,MCU的支撑电路一般需要外部时钟来给MCU提供时钟信号,而外部时钟的频率可能偏低,为了使系统更加快速稳定运行,需要提升系统所需要的时钟频率。这就得用到锁相环了。例如MCU用的外部晶振是16M的无源晶振,则可以通过

- 关键字:

简析 初始 控制 相环

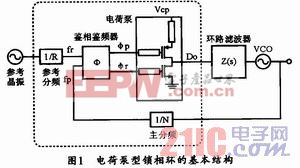

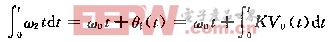

- 摘要:环路滤波器是锁相环中的一个关键模块,对宽带高压VCO进行调谐时,常采用有源滤波器。在论述了电荷泵锁相环基本原理的基础上,对有源环路滤波器的结构以及滤波器对锁相环性能的影响进行了分析,推导出有源环路滤

- 关键字:

滤波器 设计 环路 有源 电荷 相环 基于

- 摘要:为测量锁相环锁定时间,通过比较各锁相环芯片的接口特点,设计通用的测量系统。该系统包括上位机、下位机软件以及基于AT89C 51的控制电路,上位机和下位机使用串口通信。通用性和实时性是系统最大特点,在软件

- 关键字:

测量 系统 设计 时间 锁定 MCU 相环 基于

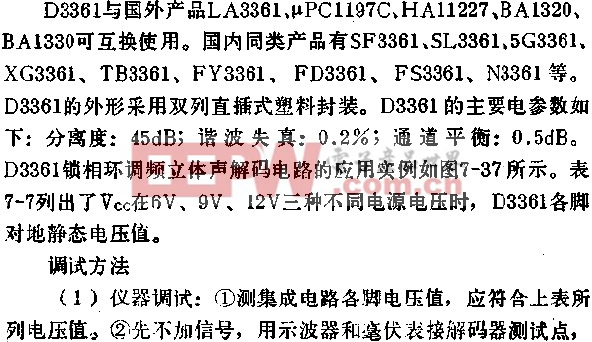

- D3361调频立体声解码电路,采用锁相环方式解码,它比D3301解码电路多了一个锁相环电路,因此性能较D3301优越.主要是提高了解友分离度,减小了解调失真.该电路电源电压范围宽,3~6V均可正常工作.

- 关键字:

D3361 应用 电路 解码 调频 立体声 相环

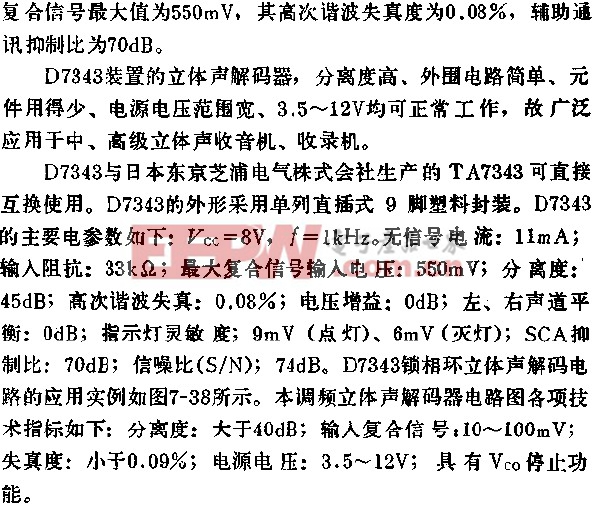

- D7343锁相环立体声解码电路与D3361内部电路大同小异,其差别在于D7343用触发器来控制立体声开关接通,当复合信号较小时触发器不翻转,这时变为单声道.用这种方式控制开关的立体声解码器的信噪比较同类型解码器好,S/N大于

- 关键字:

D7343 应用 电路 解码 调频 立体声 相环

- 摘 要

电荷泵锁相环的锁定指示电路设计,常用的方法是在PFD 电路中通过检测经分频后的参考输入和本振反馈信号的相位误差来实现,当相位误差超过某个锁定检测窗口时,锁相环电路就上报失锁告警。由于数字锁定指

- 关键字:

电路 应用 分析 检测 锁定 相环 数字 电荷

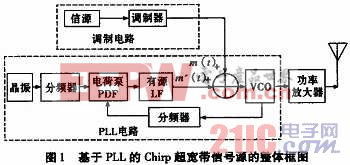

- 摘要:在传统的模拟法产生Chirp超宽带信号的基础上,提出了一种基于锁相环(PLL)法的Chirp超宽带信号源设计方案。与传统的模拟方法相比,该方法产生的Chirp超宽带信号载频稳定性高,能够达到参考信号的频率稳定度。从

- 关键字:

设计 实现 信号源 宽带 相环 Chirp 基于

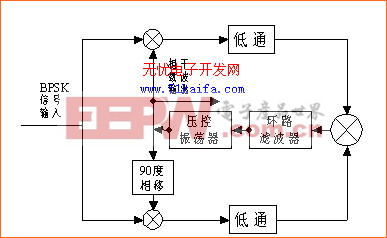

- 基于DSP的高阶COSTAS锁相环的设计,COSTAS环是一种闭环自适应系统,用于提取相干载波。本文主要介绍了一种用于载波同步的高阶COSTAS环路,用于完成MPSK的相干解调中的载波同步。本文提出了一种便于软件实现的COSTAS环路的简化结构,用于完成8PSK的载波

- 关键字:

相环 设计 COSTAS 高阶 DSP 基于

- 基于ADF4106的锁相环频率合成器,介绍了锁相环路的基本原理,分析了集成锁相环芯片ADF4106的工作特性,给出了集成锁相环芯片ADF4106的一个应用实例,为高频频率合成器的设计提供了很好的思路。

关键词:ADF4106,锁相环,频率合成器,环路滤波器

- 关键字:

合成器 频率 相环 ADF4106 基于

- 本文介绍的基于锁相环的可变量程转速控制系统,是为研制新一代具有卷绕特性的调速电机控制器而开发的[1],其转速信号检测方法具有结构简单、安装方便、价廉可靠的特点。 1 PLL电机转速控制系统原理 用锁相环路

- 关键字:

控制系统 转速 变量 相环 基于

- 摘要:电荷泵型锁相环的设计主要集中在环路滤波器。为了解决各种环路滤波器对锁定时间要求较高,并在环路带宽较宽的应用中对参考频率附近杂散抑制不够,因而致使锁相环相位噪声及杂散恶化的问题。文中以ADF4117为基础

- 关键字:

设计 相环 电荷 ADF4117 基于

- 随着大规模集成电路技术的发展与成熟,CMOS工艺以其低成本、低功耗、高集成度的优点使得采用CMOS工艺实现高性能集成锁相环具有十分重要的意义和广阔的前景。

- 关键字:

芯片 设计 相环 电荷 CMOS 工艺 基于

- D7343锁相环立体声解码电路与D3361内部电路大同小异,其差别在于D7343用触发器来控制立体声开关接通,当复合信号较小时触发器不翻转,这时变为单声道.用这种方式控制开关的立体声解码器的信噪比较同类型解码器好,S/N大于

- 关键字:

电路 应用 解码 立体声 相环 调频 D7343

- D3361调频立体声解码电路,采用锁相环方式解码,它比D3301解码电路多了一个锁相环电路,因此性能较D3301优越.主要是提高了解友分离度,减小了解调失真.该电路电源电压范围宽,3~6V均可正常工作.

- 关键字:

电路 应用 解码 立体声 相环 调频 D3361

- 提出一种设计全数字锁相环的新方法,采用基于PI控制算法的环路滤波器,在分析模拟锁相环系统的数学模型的基础上,建立了带宽自适应全数字锁相环的数学模型。使用DSP Builder在Matlab/Simulink环境下搭建系统模型,并采用FPGA实现了硬件电路。软件仿真和硬件测试的结果证明了该设计的正确性和易实现性。该锁相环具有锁频速度快、频率跟踪范围宽的特点。同时,系统设计表明基于DSP Builder的设计方法可缩短设计周期,提高设计的灵活性。

- 关键字:

相环 设计 实现 数字 适应 DSP Builder 带宽 基于

相环介绍

您好,目前还没有人创建词条相环!

欢迎您创建该词条,阐述对相环的理解,并与今后在此搜索相环的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473