嵌入式逻辑分析仪在FPGA时序匹配设计中的应用(07-100)

——

使用Signal Tap II时应注意:

本文引用地址:https://www.eepw.com.cn/article/81757.htm·用Signal Tap II 采集数据时,应符合采样定律,即采样频率必须是信号最大频率的两倍或更高,否则采集到的波形会失真或者是一条全低的直线。

·采样深度决定了每个信号可存储的采样数目,信号的数量和采样深度的乘积不能超过所选FPGA芯片内部RAM的大小,添加待观察信号、设置了采样深度后,可以根据Signal Tap II的Instance Manager 窗口观察内部存储资源的使用情况。如果观察的信号数量多,采样深度设置受到限制,此时灵活设置触发条件相当必要。图4和图7采集的波形都是以设置RGBdin[23..16]为00h为触发条件,如图4,7中的虚线所示。

·Signal Tap II必须工作在JTAG方式,调试完成后应将Signal Tap II文件移除,以免浪费FPGA资源。

结语

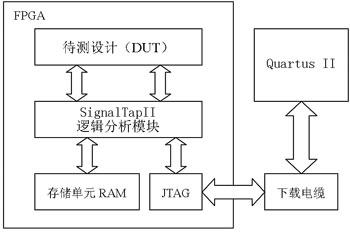

时序匹配是FPGA电路设计中的一个重要问题,介绍了一种应用嵌入式逻辑分析仪Signal Tap II捕获FPGA内部信号波形的方法,通过比较分析采集的数据,可得出精确的延时信息,指导FPGA时序匹配的设计。

以LED全彩大屏同步显示控制系统中显示驱动控制部分的位面分离模块为例,在嵌入式逻辑分析仪Signal Tap II的时序测试结果的指导下,设计一个由34个D触发器构成的时序匹配模块,经实际电路的波形测试证明,信号时序匹配良好。

评论