互连时序模型与布线长度分析

2.时序分析实例

本文引用地址:https://www.eepw.com.cn/article/274626.htm2.1 MII接口

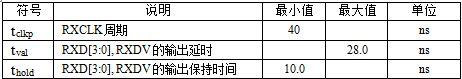

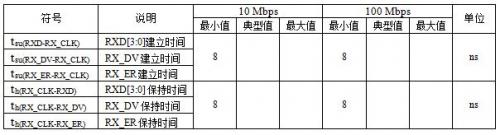

MII接口是最常用的百兆以太网PHY芯片与MAC间的接口,表1和表2分别是某百兆PHY芯片和某MPU内部MAC的RX通道时序参数表。

表1某PHY芯片RX通道时序参数表

表2某MPU内MAC RX通道时序参数表

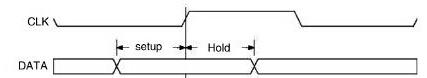

通过表格可以看出,MAC侧要求RXD、RX_DV和RX_ER信号对RX_CLK信号的建立与保持时间最小为8ns,也就是实际的建立与保持时间不得小于8ns.假设RXD、RX_DV与RX_CLK信号从PHY侧到MAC侧的延时完全相同,则在MAC侧有:

传输的时钟周期为40ns;

最小的建立时间为40-tval =12ns;

最小的保持时间为thold = 10ns;

最小的建立时间和保持时间总和为22ns;

假设RXD、RX_DV和RX_ER信号对RX_CLK信号存在延时,则存在两种极端情况:

当延时导致建立时间达到最低要求,即当相对延时为+4ns时,则在MAC侧建立时间为8ns,保持时间为14ns;

当延时导致保持时间达到最低要求,即当相对延时为-2ns时,则在MAC侧建立时间为14ns,保持时间为8ns;

假设MII接口走线在PCB表层,PCB板材为FR-4,可知信号传输速度大约为160ps/inch,综合上述两种情况,可以得出RXD、RX_DV和RX_ER相对RX_CLK的走线长度关系为:延迟+4ns时,RXD、RX_DV和RX_ER走线相对RX_CLK可以长:4000/160 * 2.54 = 63CM;延迟-2ns时,RXD、RX_DV和RX_ER走线相对RX_CLK可以短:2000/160 * 2.54 = 32CM;可见,对于MII的RX通道信号,可以无需考虑等长。

注意,时序关系不代表不需要考虑反射问题。当信号在走线上的传播和返回延时比信号的上升时间长时,就有必要考虑是否进行终端阻抗匹配以抑制反射。

下面使用公式进行计算,以对比理论分析和公式法的优劣。为简化计算,忽略公式(1)和公式(2)中的抖动因素Tjitter-clk和Tjitter-data,相关公式变为:

(Tsetup)min + (Tco)max + (Tflt-data - Tflt-clk)max(Thold)min(6)

将表2和表3中的参数带入公式(5)和公式(6),得出:

10 - (Tco)minflt-data - Tflt-clk< 4

由于PHY芯片参数并没有给出(Tco)min这个参数,所以公式无法得到最终结果。由于PHY芯片的最长输出延时为28ns,最短保持时间为10ns,在此假设(Tco)min为12ns,则:

-2flt-data - Tflt-clk< 4

可分解为:

Tflt-data - Tflt-clk< 4

Tflt-clk-Tflt-data< 2

换算成长度就是:

Lflt-data - Lflt-clk<63CM

Lflt-clk -Lflt-data<32CM

可以看出,使用公式分析时有时会受到参数不全的制约,这时需要根据其他参数推断出需要的参数。对比分析法和公式法,可以看出:分析法比较繁琐,需要认真分析时序关系,而公式法却非常快捷。不过,公式法有时会受到参数的制约,得不到全面的结论。实际中,应该两种方法结合使用。

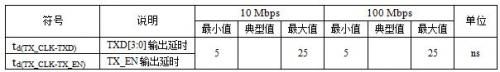

下面分析该PHY芯片和MAC间TX通道的时序。表3和表4分别是该百兆PHY芯片和MPU内部MAC的TX通道时序参数表。

表3 某PHY芯片TX通道时序参数表

表4 某MPU内MAC TX通道时序参数表

使用公式进行计算,为简化忽略公式(3)和公式(4)中的抖动因素Tjitter-clk和Tjitter-data,则相关公式变为:

(Tsetup)min + (Tco)max + (Tflt-data)max + (Tflt-clk)min

< T

(Thold)min< (Tco)min + (Tflt-data)min + (Tflt-clk)max

带入上述参数表中的参数,化简得到:

Lflt-data + Lflt-clk< 47.625CM

假设MII走线在PCB表层,PCB材料为FR-4,走线传输速度为160ps/inch,综合上述分析,可以得出TXD、 TXEN 分别和 TXCLK的走线之和不能大于47CM。实际布线中,本组走线应当越短越好。走线越短,则数据的建立时间越充足,保持时间越少。本实例中,恰好MAC侧允许保持时间为0ns。

评论