Wide I/O、HBM、HMC将成存储器新标准

现行的DDR4及LPDDR4存储器都是以既有的DRAM设计为基础,其中许多技术已沿用长达十余年,而今无论是系统总频宽或中央处理器(CPU)等作业环境都不可同日而语。有鉴于此,发展新的解决方案为眼下业界的共识,Wide I/O、HBM及HMC等三大新存储器标准遂成业界关注重点。

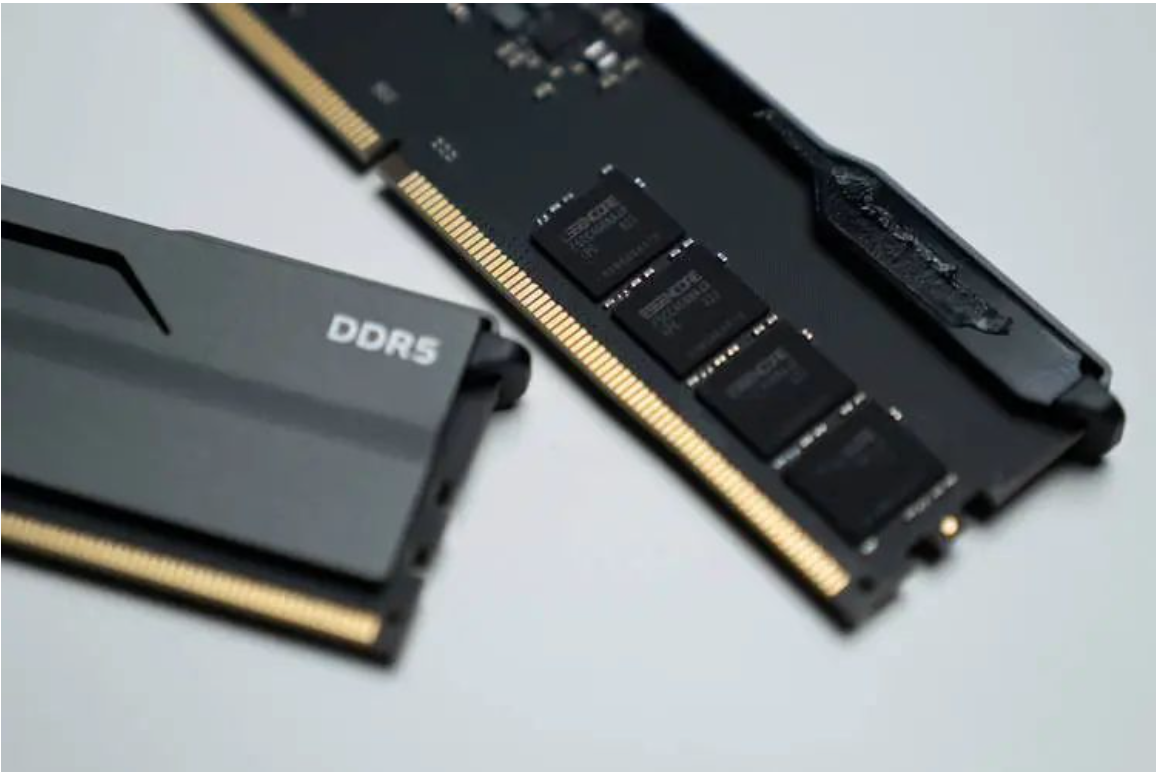

本文引用地址:https://www.eepw.com.cn/article/270147.htm据ExtremeTech网站报导指出,过去近20年来存储器规格已从第一代的SDRAM DIMM发展至DDR4-3200,成长高达48倍。因此,现今业界虽针对是否应进一步以此标准定义DDR5有所争议,更多人却倾向发展新的存储器标准。

Wide I/O的设计旨在为移动系统单芯片(SoC)提供高频宽、低功耗的存储器,主要吸引的是智能型手机及嵌入式系统公司,目前的发展主力为三星电子(Samsung Electronics)。

Wide I/O为此标准的第一代版本,符合JEDEC规格,然预计会正式普及到市场的应是第二代的Wide I/O 2。三星投注大量心力在此技术研发上,目前虽未有明确的时程目标,但2015年下半可望看到初步成果。

另一项标准则为英特尔(Intel)及美光(Micron)共同主导的混合存储器立方体(Hybrid Memory Cube;HMC),拥有超大频宽,但功耗与成本也较Wide I/O 2有过之而无不及。英特尔与美光表示,HMC频宽可达400GB/s,预计将于2017年开始商业应用。

HMC除了是最为昂贵的新标准外,还拥有一大发展目标,亦即摆脱现行DIMMS的二重控制逻辑,简化设计,采用3D堆叠技术,并以单一控制逻辑层处理所有读写流量。

专为图像处理器(GPU)设计的则为另一款高频宽存储器(High Bandwidth Memory;HBM)标准,目前超微(AMD)及NVIDIA皆计划从下一代GPU开始采用此标准,其中NVIDIA预计将以2016年推出的Pascal为此标准的首波代表。

未来采用HBM标准的GPU在主要存储器频宽上可望达到512GB/s,与目前的336GB/s相比高下立见。在成本与频宽两方面,HBM都算是“中庸”之选,且有可能抢在三星推出Wide I/O 2前率先问世。

总体而言,传统的DDR标准虽然价格可亲,但能源功率相对较差;后起之秀Wide I/O 2、HBM及HMC等虽强化了功率及频宽,但因成本居高不下,现阶段仍只能做为企业或图像处理应用。

不过毋庸置疑的是,这三项崭新的存储器标准势必会在存取速度及整体效能上带来重大突破,为业界掀起一波新的存储器旋风。

存储器相关文章:存储器原理

评论