信号链基础知识之模拟正交调制器失衡的数字校正

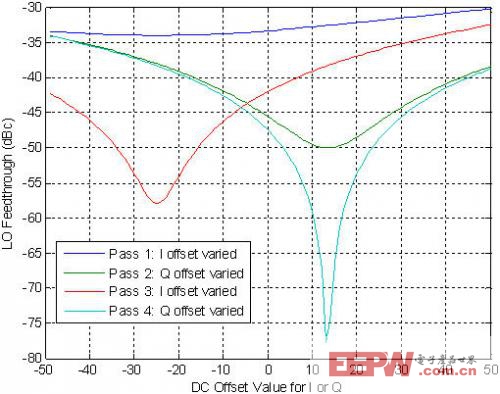

通过在基带信号中添加一个反向偏差,可对LO馈通进行校正。许多双高速DAC或集成发射器解决方案,例如:TI的AFE7071等,都包括生成校正用基带偏差的数字电路。找到I和Q基带信号最佳DC偏差值的一种简单方法是,监测LO馈通振幅,并反复地改变首个I DC偏差,然后再改变Q DC偏差,最终找到最小LO馈通(图3)。在pass 1期间,Q DC偏差保持不变,而对I DC偏差进行扫描,直到找到最小LO馈通为止。在pass 2期间,I DC偏差值维持在最低限度,而对Q DC偏差进行扫描,直到找到最小LO馈通为止。在理想情况下,每个I和Q仅需要一个pass,但首批2个pass期间LO馈通最小值所产生的测量误差,通常亦意味需要3个或者4个pass。

本文引用地址:https://www.eepw.com.cn/article/259863.htm

图3:本机振荡器馈通校正过程

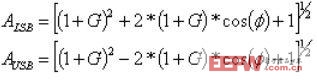

增益和相位误差会导致无用混频器抵销不完全的结果—剩余量称作边带抑制(SBS)。上下边带振幅以基带Q输入的增益误差G和I分支混频器LO的相位误差(弧度)作为开始,其为

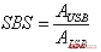

在这种情况下,低边带主导,而边带抑制为一个比率:

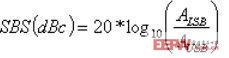

或者也可以用dBc表示:

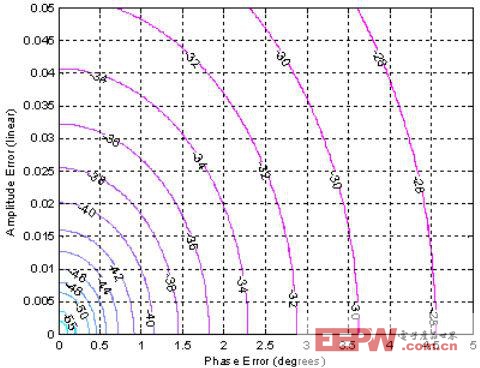

图4显示dBc和相位及振幅误差表示边带抑制的比较情况。

图4:边带抑制(dBc)对比相位及振幅误差

评论