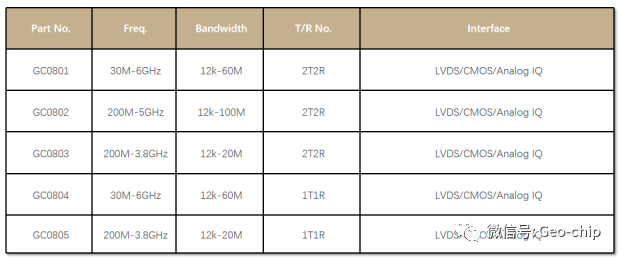

认知无线电:现场可编程射频器件提供突破性的机会

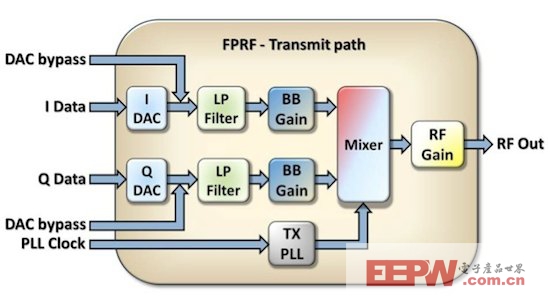

在发送侧,基带电路提供由流进DAC的IQ数据调制的射频输出。在收发路径上芯片都有滤波器,这些滤波器可以针对各种不同带宽进行编程。这样就可以将信号限制在感兴趣的带宽内,并衰减掉由数据转换器引入的不可避免的混叠和量化噪声。每个放大器均可提供可编程的增益,同时芯片针对接收到的信号提供低噪声放大器(LNA)选择。器件可以通过串行接口(SPI)连接进行编程,因此操作非常方便快捷。

图2:FPRF发送功能框图。

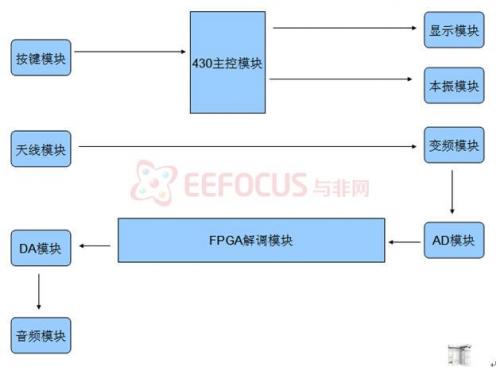

这份简要说明应该介绍一下为什么Lime的FPRF器件适合认知无线电。这种器件能够满足灵活、频率多变设备的低功耗和经济性要求。在大多数应用中,数字处理和控制是由现场可编程门阵列(FPGA)完成的。

图3:FPGA和FPRF为认知无线电系统提供了一个平台。图中由Nuand公司提供的电路板将Altera的FPGA和Lime的FPRF整合在一起。

图3:FPGA和FPRF为认知无线电系统提供了一个平台。图中由Nuand公司提供的电路板将Altera的FPGA和Lime的FPRF整合在一起。

FPGA 可以用来解码由FPRF芯片输出的数字IQ数据,也可以用来编码该数据进行发送。使用FPGA执行基带功能的硬件加速任务的优势是,它可以针对 没有现成ASSP器件可用的演示系统进行设计,比如认知无线电系统这种情况。设计可以加以定制以适合系统,而且由于逻辑部分在操作期间可以进行动态重配 置,所以能够实现某种复杂的硬件加速效果。例如,逻辑部分可以经过重配置产生IQ数据,进而在信道的信噪比较差时提供正交相移键控 (QPSK),或者在信号条件较好的情况下提供正交幅度调制(QAM)实现更快的数据传送。即使低成本FPGA也有的另外一个优势是,它们包含复杂的时钟 管理模块。这些模块可以通过整合模拟PLL或数字锁相环(DLL)提供频率综合和相移功能。低抖动时钟发生和抖动滤波功能则可以用来产生时钟,进而驱动 FPRF的收发PLL,满足要求不太严格的应用需求。

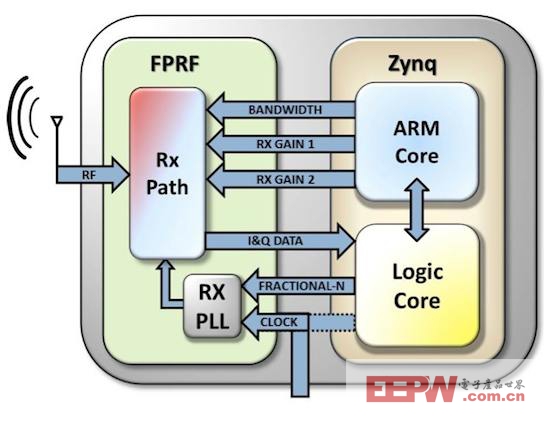

FPRF芯片逻辑和参数的重配置智能是由系统处理器上 运行的软件提供的。赛灵思和Altera公司的器件都包含高性能ARM处理器,并作为硬件内核的方式嵌入在里面与可编程逻辑放在一起。这样就有机会减少芯 片数量并提高系统性能。下面的文字描述介绍了将赛灵思的Zynq器件用作基带芯片的概念。之所以选择Zynq是因为在ARM和可编程逻辑之间有多条快速片 上连接和数据总线可提供高带宽。另外,诸如Linux等操作系统(OS)支持、设计和调试工具以及用于设计可编程逻辑和ARM组合的全面支持生态系统也都 是现成的。

在认知无线电中,第一步操作是扫描空中电波是否有免费频率。Zynq器件上的处理器按顺序设置FPRF中的带宽和 增益控制,并使用SPI接口加载寄存器(图中为了看得清楚将它们显示为单独的路径,实际在四线SPI上使用了时分复用技术)。ARM处理器和可编程逻辑内 核的组合用于通过SPI改变接收PLL上的小数N和频率值。这样就能让Zynq经过所有信道,而接收到的IQ数据提供了信号的瞬时电平。可编程 逻辑一般用于处理来自FPRF器件的数据,ARM软件可以被编程为暂停在信号低于预定义电平的任意信道上。如果需要的话,Zynq还能调整增益或带宽以确 保信道没有业务。需要的话,系统还能在整个过程中通过多次扫描来建立当前的业务图案。

图4:FPRF接收器在软件控制下扫描免费信道,并锁定到所选的频率。

一旦状态确定,认知无线电就能发送它所选择使用的频率、带宽和调制方案,并且可能在专门针对这些数据的预定信道上发送。FPRF能够支持全双工操作,一旦在认知无线电的发送和接收端之间相互同意所用的收发信道、带宽和调制方案,系统就能切换到这些设置。

评论