采用CMRC结构的Ka波段 四次谐波混频器设计

4.3 本振滤波器设计

在本振输入端,应该通本振(9.6GHz),阻射频(37.5GHz)、本振奇次谐波(3LO=28.8GHz、5LO=48GHz)、射频与偶次本振的谐波(RF-2LO=18.3GHz)。

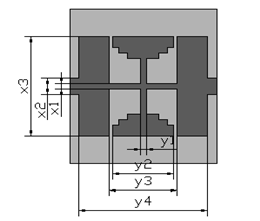

同中频低通滤波器设计类似,也采用两个CMRC级联形式,其中一级长度也选2.6mm,二级长度选1.6mm,级联后HFSS仿真结果如下:

图8 本振端滤波器仿真结果

它对20GHz以后的频率都有了20dB以上的抑制,很好满足了设计的要求。

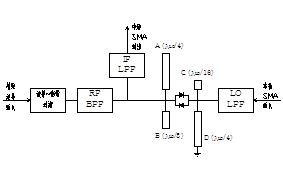

5 整体电路设计

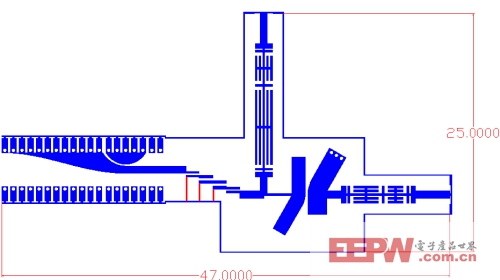

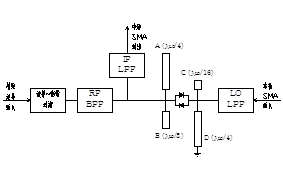

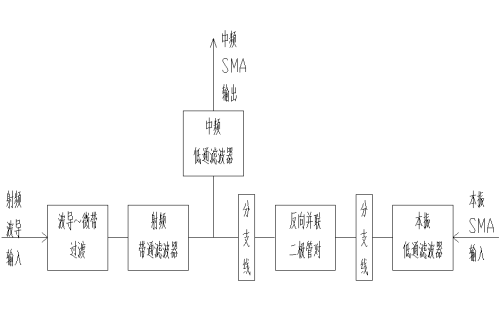

最后,经过优化设计的整体电路如图9。电路左侧为射频输入,右侧为本振输入,中频由上端输出。

图9 整体电路加工图

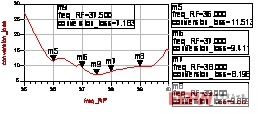

结合HFSS和ADS,仿真得变频损耗随射频输入频率变化结果如图10:

图10 Ka波段四次谐波混频器变频损耗

由图可见,15dB以下变频损耗带宽约有4.5GHz,最低变频损耗为7.2dB。

6 总结

本文介绍了谐波混频器的基本原理,分析了CMRC结构的慢波、宽带阻特性,据此设计出一种性能良好的Ka波段宽频带四次谐波混频器。变频损耗在15dB以内的带宽有4.5GHz。在射频频率37.5GHz,本振功率10dBm,中频频率900MHz时,变频损耗为7.2dB。实验研究工作正在进行中。

基金项目:国家自然科学基金委创新群体基金(60621002)

评论