NI矢量信号收发器的FPGA编程

图 7. RF输入回路以可配置I/Q速率生成已校准数据,并将其写入DRAM。

RF输出循环类似于RF输入循环,但是操作顺序相反。来自DRAM的数据进行内插、定标、频移、相位校准、内插、校准,然后通过数模转换器(DAC)生成。另外还有触发和同步所用信号。

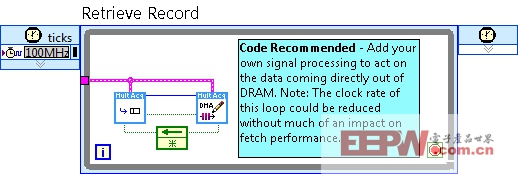

图 8. RF输出循环检索来自DRAM的数据然后生成数据

过程子VI包含有循环和状态机,实现了多数据记录采集和DRAM控制器对波形的排序。这些子VI包含了大量代码,满足了大带宽和低滞后性能 要求,确保这些子VI能够在全速率ADC数据转换下溢出,以及产生全速率DAC数据而不发生下溢,同时仍然与主机之间进行波形数据传输。

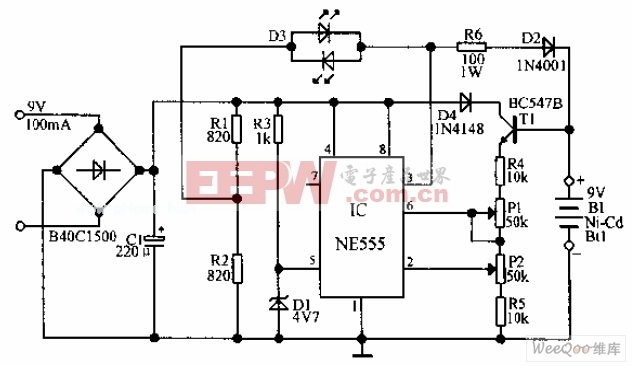

读取循环实现的功能可以存在于多记录采集过程之内,然而为了方便起见而将其显示出来。该循环可以再数据离开DRAM时并在被发送到主机前进 行数据处理。此路径在它自己的回路之内,从而那些并不符合120 MHz RF输入和输出回路的定时要求的IP仍然可以使用。为了适应这种IP,稍微降低此回路速率并不会影响读取性能,然而如果降得过多,则只会增加数据到达主机 所需时间。这样即使采样内存被填满了,也不会丢失样点或破坏数据。

图 9.读取循环提供了在已采集数据返回主机之前对其进行处理的机会。在默认情况下,读取回路返回原始数据。

评论