3G手机技术发展与设计架构(4)

新一代的3G手机标榜着更丰富多元的应用功能,以及更佳的移动影音效果,这虽是令消费者很期待的诉求,但要落实到手机的设计上时,除了要在有限空间中塞入更多元件的难题外,也得克服功耗设计上的瓶颈。过去的语音通话战友用的运算资源有限,只需采用低时脉的微处理器即可运作,但新的3G多媒体手机中,陆续整合中的Bluetooth、Wi-Fi、A-GPS、Mobile TV等通信功能,将增加射频/基频的处理功耗;视频电话、电视或3D游戏,则会大幅提升应用处理器的运算负荷;此外,採用更大的萤幕及更佳的解析度,也会造成系统功耗的沈重负担。这些,都和多元功能的诉求背道而驰。

如果电池的容量能够有所突破的话,或许还能疏解手机对电力供应上的飢渴需求,但实际的情况是电池供电力虽逐年有提升,但远远比不上移动设备对供电需求的成长。就SIA在2002年更新发表的技术发展蓝图来看,最大电池供电力与容量平均每年成长10~15%,但手机系统的电力需求却是以每年35~40%的需求比例在成长中。在此情况下,手机耗电与电池供电的差距只会不断地扩大。

在电池电力难以相应提升的情况下,手机业者只好想尽办法做出最低功耗的设计,也就是从节流的角度,从最微小的电晶体层级到晶片电路规划、再到系统层级的记忆体读写,以及软、硬件架构及演算法等各个面向,一一去做到低功耗、低洩露的省电策略及电源管理模式。以下将从不同的层面来探讨3G手机的低功耗设计议题。

■动态与静态功耗

根据2005年ITRS(International Technology Roadmap for Semiconductors)的预估,到了2008年时,高效能晶片的电路闸长度(gate length)等实体性参数将会比2005年时的数值缩减一半,但同时这些晶片的供电需求也将会增加。在发展蓝图报告的结论中指出:「耗电的增加来自于更高的晶片作业频率、更高的互连总体电容及电阻,以及由级数成长的晶片中电晶体增加的电路闸洩漏。」

要了解电子系统的耗电议题,需从动态功耗(Dynamic Power)和静态功耗(Static Power)两个面向来看。一个半导体元件的耗电,即是这两项功耗的加总:

Ptotal=Pdynamic+Pstatic

其中动态功耗是在运作模式中产生的功耗,此时信号值在切换、类比电路处于改变状态,也就是此元件正在操作某项应用功能,它可定义为:

Pdynamic=Capacitance × Voltage2 × Frequency

从这个方程式中我们可以看出,动态功耗来自于负载电容充放电和电流的切换,其中电压与功耗是平方关系,对功耗的直接影响最大,也就是说电压愈高,相对的功耗也会以级数上升;高速的频率同样也是提升功耗的杀手。因此降低电压与时脉是节省动态功耗的基本策略。

静态功耗则是当元件处于待机状态时产生的功耗,可表示如下:

Pstatic=f(leakage current)

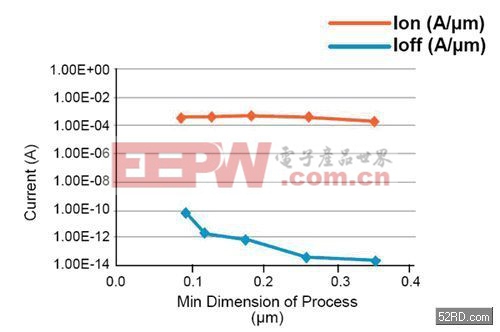

静态功耗是洩露电流状况的涵数,它和使用的制程、晶片尺寸和电晶体中的电压有密切关系。当元件处于待机休眠状态时,电路本身难以避免会产生微小的电流释放,造成持续性的耗电。在过去的微米时代,动态功耗是手持设备耗电的主因,静态功耗的影响极微,但随着制程的微缩,静态的洩露电流持续上升,在进入90奈米后,静态功耗的提升更为快速,已是不容忽视的耗电课题。请参考(图一)。

▲图一:静态的电流洩露状况随制程进展而趋于严重。

■电源管理模式

从以上的分析可以清楚地知道,在电子产品的耗电上,主要来自于电流洩露(current leakage)、电压上升,和时脉频率的提升。因此想进行低功耗的设计,就得从这此三点来下手。其实降低耗电的不二法门,就是不需用到电的地方,就让它休息,但要用时,又要尽快把它叫醒。因此,就手机的系统层面来看,会区分出主处理器、周边和PLL等不同的区域(Domain),并视设备的工作现况而进入不同程度的省电模式。

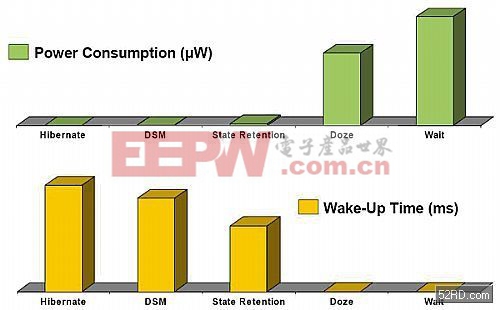

目前市场上各家厂商所提供的省电模式大同小异,我们以Freescale的i.MX31/i.MX31L应用处理器平台为例,它总共分为六种供电操作模式,当进入愈深度的休眠状态,所需唤醒的时间就会愈长,如(图二)所示。这六种模式分别是:

1.运作(Run):一般运作状态,以频率及电压的管理来提供省电机制。

2.待机(Wait):在此模式中,主处理器的时脉会停止,但是汇流排交换器和周边的时脉还保持在运作状态。

3.打盹(Doze):主处理器和汇流排交换器都停止,透过对时脉控告器(clock controller)模组的预先设定,一些特定的周边也能在此模式时自动的关掉时脉供给。此模式的恢復运作时间很短。

4.状态保留(State Retention):此模式下所有的时脉都会关掉,PLL也会停用,外部的记忆体被设定为低功耗模式(self-refresh)。此模式比Doze模式还要省电,叫醒时间较长,但在叫醒后不需恢復任何资料。

5.深度睡眠(Deep Sleep Mode;DSM):在此模式下,整个主处理器平台的电源供应都会被关掉,所有相关的暂存器资料都必须先做存档动作。此模式也称为WFI(Wait-for-Instruction)。

6.冬眠(Hibernate):整颗IC的供电都停止,所有内部的资料必须先存到外部的存储器当中。

▲图二:不同省电模式的耗电与唤醒时间比较。

以ST的Nomadik来说,也有类似的待机省电模式,以及相应的技术策略。Nomadik採用时脉闸控(clock-gating)和运算子隔离(operand-isolation)技术来关闭晶片中非活动的部分。为了降低静态耗电,晶片中除了即时时脉(Real Time Clock;RTC)和电源管理单元(PMU)外,其他的电路都可以处于不供电状态,但可以在3ms内重新开始运作。

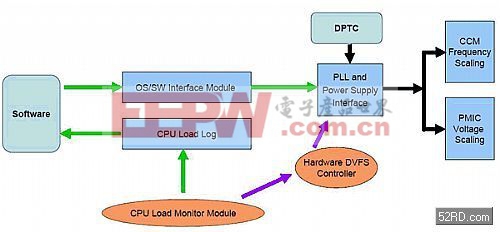

在动态功耗上,可以针对晶片中不同的区域,依工作需求而提供不同的时脉与操作电压。例如Freescale即提出动态程序温度补偿(Dynamic Process Temperature Compensation;DPTC)和动态电压频率缩放(Dynamic Voltage Frequency Scaling;DVFS)两项技术。其中DPTC可根据当下的温度和所使用的制程来动态调整供电电压;DVFS则能将操作电压降低到所需使用的最小等级,以支援特定时间中执行该项应用功能的最小操作频率。

▲图三:DVFS的运作示意图。

不过,採用低驱动电压虽有助于降低耗电,但随着制程的微缩,目前供给电压(Supply Voltage)与临界电压(Threshold Voltage)已相当接近,能在下降的空间已经有限。此外,想降低电压又不影响功率,只能提高电流量,这又会导致电流洩露与造成信号不稳定的EMI等议题。

还有一些作法能有效降低电路层级的功耗。其中一种作法是从个别电路闸的功耗(power-per-gate)去下手。应用处理器的厂商会在电路中採用两种特殊的电晶体,即高临限电压(high-Vt)和低临限电压(low-Vt)电晶体。其中低临限电压是一种高速但电流洩露相对较高的电晶体,它适合用在强调效能表现的关键性时刻;高临限电压则是一种低速和低洩露性的电晶体,它能藉由降低电路关闭下的电流洩露来延长电池的寿命和预备(standby)的时间。

■提升效率=降低功耗

除了上述多层次的省电模式及从电路层级进行低功耗设计外,3G手机想降低整体的功耗,还得从系统架构面去进行妥善的规划。在手持设备中,採用高时脉的处理器并不一定就能获得理想的运算效能,但肯定会降低电池的寿命,并产生高热的问题。因此,如何在效能与功耗之间取得最佳的平衡,就得靠系统架构的规划来决定。

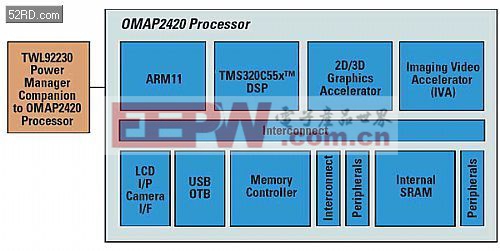

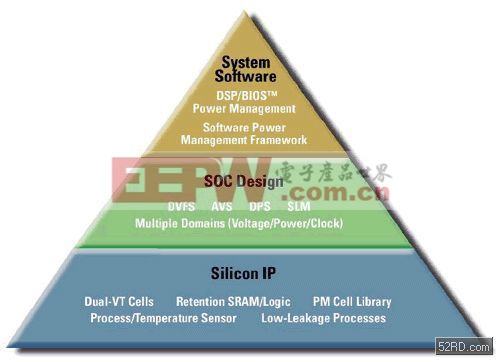

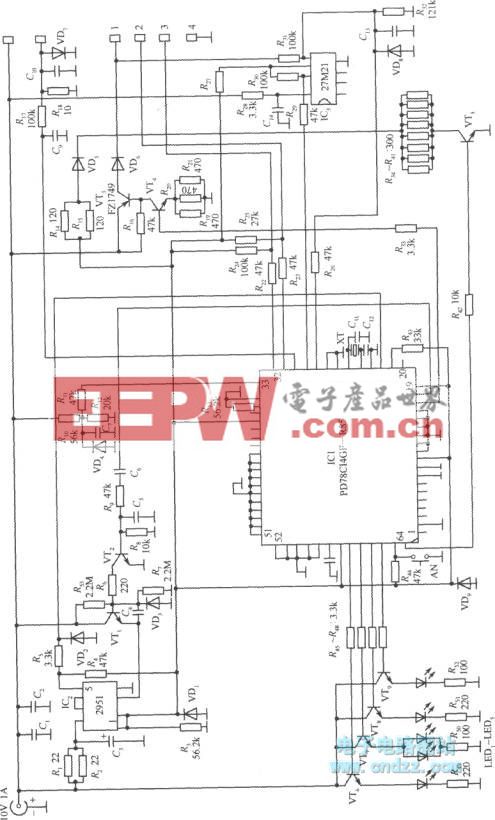

「专业分工」是3G手机系统的必然发展趋势,因为此举能在提升效率的同时,也降低了系统的功耗。这包括通讯功能与应用功能分别由专属的单元来处理;依工作性质的不同,交给最适合的处理器核心来执行,例如将控制功能交给RISC主处理器核心(如ARM),大量的信号运算则交给DSP,甚至可以采用专属的软、硬年加速单元来进一步提升运算效能的功能,如视频、音频、3D、影像等加速器或外挂的多媒体晶片。此外,应用处理平台会与电源管理单元(PMU)密切整合在一起,以达到上述的省电机制,请参考(图四)。

▲图四:应用处理器与电源管理单元的整合架构(以TI OMAP2420为例)。

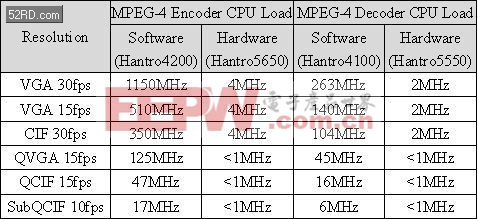

以MPEG-4编码为例,如果要做到30fps的VGA画质,用软件跑要用掉1GHz以上的CPU资源,用此种作法来处理视频内容,一下子就会把电池的电力耗尽;但若采用硬件加速器,则只需要数MHz的CPU资源即可。加速器能独立地与区域DMA和存储器资源一起工作,在此种平行运算的架构下,主核心可以用来执行其他更关键的控制与程式流(program-flow)任务,或是进入省电模式来延长电池寿命。

▲硬件加速器与CPU资源使用比较表。

目前有两种指令方式能在不冲击效能的条件下以较低的频率操作,进而有助于降低功耗,一是单指令多重资料指令集(single-instruction-multiple-data;SIMD),它能达成影像编码(image coding)演算法的资料级平行运算(data-level parallelism);另一种方式是採用超长指令集(very-long-instruction-word;VLIW)架构,它能在每个循环中同步执行多个运算动作。有些多媒体应用处理器将主处理器(RISC)和DSP或VLIW核心整合在一起,作为SIMD/Vector加速引擎。

此外,由于系统对存储器的指令读取及资料读写频繁,这种资料来往的负载电容充放电过程,也是产生耗电的一大源头。因此,妥善的规划晶片内外部的记忆体型式及对不同存储器的存取策略,也有助于降低功耗。以应用处理器来说,其常用的系统存储器包括ROM和SRAM,其中ROM具有安全存取性,而SRAM则具有较快的存取效率,也能降低I/O的耗电性和晶片上(on-chip)的需求频宽。

■结论

从事手持设备开发的业者,无不将耗电视为首要的考量议题之一,而对于任务繁重3G手机来说,省电效益更是必须严阵以待的事情。目前各大晶片厂商都致力于发展自己的低功耗技术,例如TI为其OMAP和DSP系统推出SmartReflex电源管理技术。此技术能将静态漏电大幅减少1,000倍,并能调整不同元件和系统建构模组的耗电量与效能,同时利用一组电源管理单元把电路分成多个电源区来各自管理,每一区都能切断电源,以做到零漏电的诉求。Freescale也有一套省电技术,称为Smart Speed技术架构下,它以硬件加速器减轻CPU及交叉开关(crossbar switch)的负荷,同时让系统具备平行处理功能。

▲图五:TI的SmartReflex技术採三层省电考量。

当我们随身携带一台3G手机,在讲电话、收听立体声音乐、大玩3D游戏之余,还能连续看个一、两小时的行动电视,这除了要归功于内部晶片及系统所提供的强大功能外,更不能忘却电源管理与各种低功耗设计策略也是3G手机成功的背后主要功臣。(52RD.com)

评论