典型返驰式拓扑设计——实现最佳化电源

第叁,运算一次侧电感,以保持尽可能高的右半平面零点(RHP),因而大幅地提高闭环穿越频率。

实际上,第一个标準只用于特殊情况,而选择的磁化电感可作为变压器尺寸、峰值电流和RHP零点之间的最佳折衷。

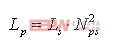

为了确定二次侧最大纹波电流来计算一次侧和二次侧电感,可用以下公式计算出二次侧电感()和一次侧电感():

(8)

公式中是开关频率,是允许的二次侧纹波电流,通常设置在约为输出电流有效值的30-50%:

(9)

那么,等效一次侧电感可从以下公式获得:

(10)

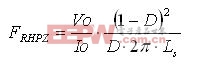

如前所述,一次侧电感和佔空比会影响右半平面零点(RHP)。RHP增加了闭环控制特性的相位滞后,迫使最大穿越频率不超过RHP频率的1/4。

RHP是佔空比、负载和电感的函数,可引发和增加迴路增益,同时降低迴路相位裕度。通常的做法是确定最差情况的RHPZ频率,并设置迴路单位增益频率低于RHPZ的叁分之一。

在返驰式拓朴结构中,运算RHPZ的公式是:

(11)

可以选择一次侧电感来削弱这种不良效果。

图3的曲线显示一次侧电感对一次侧和二次侧电流和RHP零点的影响:随着电感的增加纹波电流会减少,因此输入/输出纹波电压和电容器大小也可能减少。但增加的电感增加了变压器一次侧二次侧绕组数,同时减少了RHP零点。

图3:典型返驰式设计一次侧、二次侧纹波电流、RHP零点与一次侧电感的关係。

一般建议不应使用过大的电感,以免影响整个系统的整体闭环性能和尺寸,以及返驰式变压器的损耗。上述图形和公式只在连续导通模式下的返驰式执行才有效。

选择功率开关MOSFET并计算其损耗

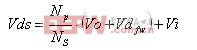

MOSFET的选择基于最大应力电压、最大峰值输入电流、总功率损耗、最大允许工作温度,以及驱动器的电流驱动能力。MOSFET的源汲击穿(Vds)必须大于:

(12)

MOSFET的连续漏电流(Id)必须大于一次侧峰值电流(公式15)。

除了最大额定电压和最大额定电流,MOSFET的其他叁个重要参数是Rds(on)、闸极阈值电压和闸极电容器。

开关MOSFET的损耗有叁种类型,即导通损耗、开关损耗和闸极电荷损耗:

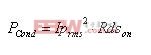

导通损耗等于损耗,因此在导通状态下源极和汲极之间的总电阻要尽可能最低。

开关损耗等于:开关时间*Vds*I*频率。开关时间、上升时间和下降时间是MOSFET闸汲极米勒电荷Qgd、驱动器内部电阻和阈值电压的函数,最小闸极电压Vgs(th)有助于电流通过MOSFET的漏源极。

闸极电荷损耗是由闸极电容器充电,以及随后的每个週期对地放电引起的。闸极电荷损耗等于:频率* Qg(tot)* Vdr

不幸的是,电阻最低的元件往往有较高的闸极电容器。

开关损耗也会受闸极电容器的影响。如果闸极驱动器对大容量电容器充电,则MOSFET需要时间进行线性区提升,则损耗增加。上升时间越快,开关损耗越低。不幸的是,这将导致高频噪音。

导通损耗不取决于频率,它还取决于和一次侧RMS电流的平方:

(13)

在连续导通模式下,返驰式执行的一次侧电流看来像图4上部所示的梯形波形。

Ib等于一次侧峰值电流:

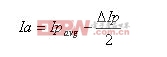

Ia是从以上的公式(5)得出的平均电流,减去一半ΔIp电流为:

(16)

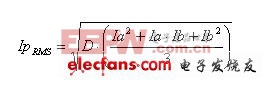

那么开关管的RMS电流可从下式得到:

(17)

或其迅速接近:

![]()

(18)

开关损耗()取决于转换期间的电压和电流、开关频率和开关时间,如图4所示。

图4:换向期间MOSFET两端的电流和电压波形。

在导通期间,MOSFET两端的电压为输入电压加反映在一次侧的输出电压,电流等于平均中间最高电流减去一半ΔIp:

(19)

(20)

在关闭过程中,MOSFET两端的电压为输入电压加反映在一次侧绕组的输出电压,再加上用于箝位的齐纳箝位电压和吸收漏电感。开关管切断电流为一次侧峰值电流。

(21)

开关时间取决于最大闸极驱动电流和MOSFET的总闸极电荷,MOSFET寄生电容器是调节MOSFET开关时间的最重要的参数。电容器Cgs和Cgd取决于元件的几何尺寸并与源极电压成反比。

通常MOSFET製造商没有直接提供这些电容器值,但是可以从Ciss、Coss和Crss值获得。

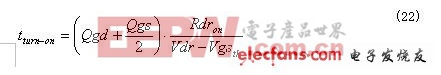

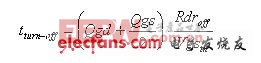

导通开关时间可以使用下列公式用闸极电荷来估计:

(22)

(23)

公式中:

Qgd是闸漏极电荷

Qgs是闸源极电荷

是当驱动电压被拉升至驱动电压时的导通时间驱动电阻

是当驱动电压被下拉至接地电压时的内部驱动电阻

是闸源极阈值电压(MOSFET开始导通的闸极电压)

缓衝器:

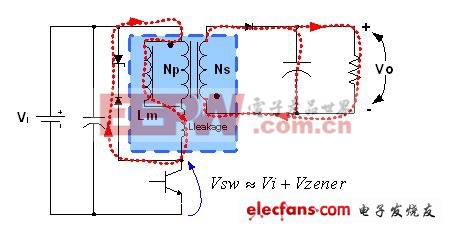

漏电感可以被看作是与变压器的一次侧电感串联的寄生电感,其一次侧电感的一部份没有与二次侧电感相互耦合。当开关MOSFET关闭时,储存在一次侧电感中的能量透过正向偏置二极体流动到二次侧和负载。储存在漏电感中的能量则变成了开关接脚(MOSFET汲极)上巨大的电压尖峰。漏电感可以透过短路二次侧绕组来进行测量,而一次侧电感的测量通常由变压器製造商给出。

耗散漏电感能量的一种常用方法是透过一个与一次侧绕组并联的齐纳二极体来阻断与之串联的二极体实现的,如图5所示。

(图5:齐纳箝位电路)

评论