基于门控时钟的低功耗电路设计方案

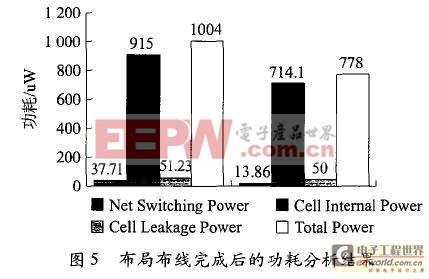

由图5可知, 采用门控时钟技术后的设计总体功耗下降了22. 6 %。其中, 开关功耗下降了63. 2 % ,内部功耗下降了21. 9 %,体现了引入门控时钟技术的优势,因为门控时钟主要用于降低动态功耗,泄露功耗略有下降。总功耗由原来的1 mW降低至778 uW,功耗降低效果非常明显。除此之外,芯片核的面积也略有减小。

3 结语

越来越多低功耗设计方法的出现为低功耗设计提供了无限的空间。门控时钟技术作为当前比较成熟的一种低功耗方法,已经得到普遍应用。本设计全面讲述了门控时钟的后端实现方法,并提出了一种门控控制项的设置方法,解决了由其引起的时钟偏移问题,对VLSI深亚微米低功耗电路物理层的实现有一定的实用价值。

评论