适用于HDTV应用的8位DAC

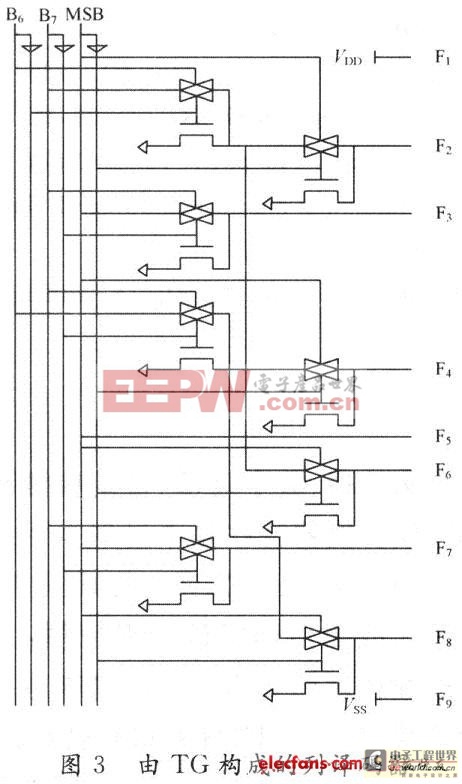

为减小功耗和减少延时,应该设计最少逻辑水平的行和列译码,运用TG逻辑电路组成3~8位行、列译码器。如此从高3位得到行译码器和从中间3位输入得到列译码器。运用TG的行译码器电路如图3所示。

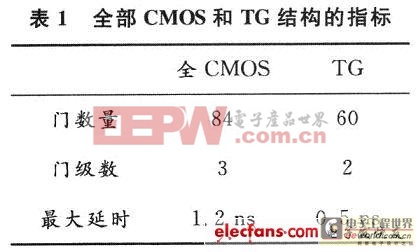

行译码器结构与列译码器基本相同,但没有电源节点。使用TG逻辑译码器的另一巨大好处是可以减少晶体管的数量。在静态逻辑,参考文献[9]的译码器由84 只晶体管组成,但用TG结构组成的行和列译码器有30只晶体管,并且总数是60。这意味着芯片面积可能也被减少。较少的晶体管级数也帮助减少延时。另一方面,使用TG结构的逻辑门最大级数可减少到2级;不使用传输门结构的全CMOS结构的最高门级数是3,以上充分说明使用TG结构更有利减少延时和改进工作频率。表1给出相关的参量对比。

2.3 工作原理

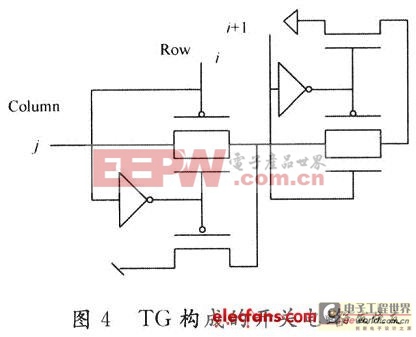

用行列译码器进行译码,单位电流源是导通还是截止,共有三种情况。第一种是所在行和下一行都是“1”,在这种情况下,无论列控制信号是否为“1”,该电流源均被选中。也就是说,对应的电流源开关状态为接通状态。第二种情况是所在的行控制信号为“1”,但是下一行的控制信号为“0”,这时,电流源是否被选中,要根据列控制信号来决定。如果列控制信号为“1”,则该电流源被选中;如果列控制信号为“0”,则该电流源不被选中,处于截止状态。第三种情况是所在行和下一行的控制信号均为“0”,那么不管其所在列的控制信号为多少,此电流源不会被选中,处于截止状态。TG构成的开关电路如图4所示。

3 电流源电路及减少毛刺电路

电流源电路是DAC的重要部分,同时为了减小毛刺反应,下面将介绍减少毛刺的电路。

3.1 电流单元

一般常用的设计均采用减少电路噪声和降低电流源的复杂结构。例如,差分电路、偏置电路、参考电流等需要很多数量的晶体管。在这个设计中,使用一个简单的电流单元结构,并且电流源采用由二只晶体管组成的电流源单元。与其他芯片相比,电路的面积可以大大减小,如图5所示。

评论