DS325X、DS316X、DS317X和DS318X中时钟速率适配器(CLAD)的使用

使用ds325x内的clad

ds325x t3/e3 liu内部的时钟速率适配器单元从单一输入时钟产生全部所需的时钟速率。如果有一路传输品质的时钟源(ds3、e3或者sts-1),时钟速率适配器可以合成出另外两种线路速率的传输品质时钟。这样,输入时钟和合成时钟都可作为主时钟用于时钟和数据恢复(cdr)单元及抖动抑制器。在liu主时钟的驱动下,cdr单元从agc/均衡器单元获得已经放大、均衡的信号,产生分离的时钟、数据正和数据负信号。在硬件模式下,时钟速率适配器完全由t3mclk、e3mclk和stmclk引脚控制。

在cpu总线模式下,通过cacr寄存器可以提供更多对于时钟速率适配器的控制。当“后备主时钟使能” (amcen — alternate master clock enable)控制位被置1时,时钟速率适配器被配置为后备主时钟模式。在这种模式下,时钟速率适配器不再工作于ds3、e3或sts-1时钟,而是工作于一个频率由“后备主时钟选择” (amcsel)控制位确定的时钟。作为后备主时钟,有效的输入频率是19.44mhz、38.88mhz和77.76mhz。在后备主时钟模式下,时钟速率适配器最多可以合成出三种时钟速率(ds3、e3或者sts-1)中的两种。要合成ds3和e3时钟,可将后备主时钟接入stmclk引脚。要合成ds3和sts-1时钟,可将时钟接入e3mclk引脚,时钟接入t3mclk引脚可以合成出e3和sts-1时钟。

尽管ds325x器件中amcen和amcsel[1:0]的上电默认值可能并不符合实际所施加的时钟,仍然可以在上电伊始就施加一个后备时钟到任一mclk引脚。上电之后一旦这些控制位被正确配置,时钟速率适配器就开始合成正确的主时钟。整个器件就可正常工作。

cpu总线模式也可以在t3mclk、e3mclk和stmclk引脚上输出一个合成主时钟,供邻近的成帧器、映射器和其他元件使用。要在t3mclk上输出合成的ds3主时钟,只需设置cacr:t3moe = 1。要在e3mclk上输出合成的e3主时钟,设置cacr:e3moe = 1,或者设置cacr:stmoe=1,在stmclk上输出合成的sts-1主时钟。

ds325x的clad配置寄存器

用于配置clad的时钟速率适配器控制寄存器的说明如下。

寄存器名称:cacr

寄存器说明:时钟速率适配器控制寄存器

寄存器地址:08h

bit 7: t3mclk输出使能(t3moe)。 当时钟速率适配器被配置为合成ds3主时钟时,通过设置t3moe = 1,可以在t3mclk引脚输出ds3主时钟。该时钟可以用作邻近的ds3成帧器和其他需要ds3时钟的元件的发送时钟。只有在t3mclk引脚没有被外部驱动时才可将该位设置为1。

bit 7: t3mclk输出使能(t3moe)。 当时钟速率适配器被配置为合成ds3主时钟时,通过设置t3moe = 1,可以在t3mclk引脚输出ds3主时钟。该时钟可以用作邻近的ds3成帧器和其他需要ds3时钟的元件的发送时钟。只有在t3mclk引脚没有被外部驱动时才可将该位设置为1。

0 = t3mclk输出驱动禁止

1 = t3mclk输出驱动使能

bit 6: e3mclk输出使能(e3moe)。 当时钟速率适配器被配置为合成e3主时钟时,通过设置e3moe = 1,可以在e3mclk引脚输出e3主时钟。该时钟可以用作邻近的e3成帧器和其他需要e3时钟的元件的发送时钟。只有在e3mclk引脚没有被外部驱动时才可将该位设置为1。

0 = e3mclk输出驱动禁止

1 = e3mclk输出驱动使能

bit 5: stmclk输出使能(stmoe)。 当时钟速率适配器被配置为合成sts-1主时钟时,通过设置stmoe = 1,可以在stmclk引脚输出sts-1主时钟。该时钟可以用作邻近的sonet成帧器、映射器和其他需要sts-1时钟的元件的发送时钟。只有在stmclk引脚没有被外部驱动时才可将该位设置为1。

0 = stmclk输出驱动禁止

1 = stmclk输出驱动使能

bit 2至bit 1: 后备主时钟选择(amcsel[1:0])。

00 = 19.44mhz

01 = 38.88mhz

10 = 77.76mhz

11 = 没有定义

bit 0: 后备主时钟使能(amcen)。

0 = 禁止后备主时钟模式

1 = 使能后备主时钟模式

使用ds316x、ds317x和ds318x内的clad

ds316x、ds317x和ds318x内的clad用于从clka引脚输入的单一参考时钟产生多种内部时钟频率(ds3、e3或者sts-1)。输入clka的时钟频率必须是以下几种之一:

ds3 (44.736mhz)

e3 (34.368mhz)

sts-1 (51.84mhz)

如果提供了上述几种时钟中的一种,就可以生成另外两种。如果需要,这些内部时钟可以驱动输出引脚clkb和clkc,供外部使用。

配置ds316x、ds317x和ds318x的clad

如果使用ds317x或者ds318x的liu,clad可以向ds317x或者ds318x的接收liu提供时钟。ds316x、ds317x或者ds318x的clad由gl.cr2寄存器中的clad位进行配置。

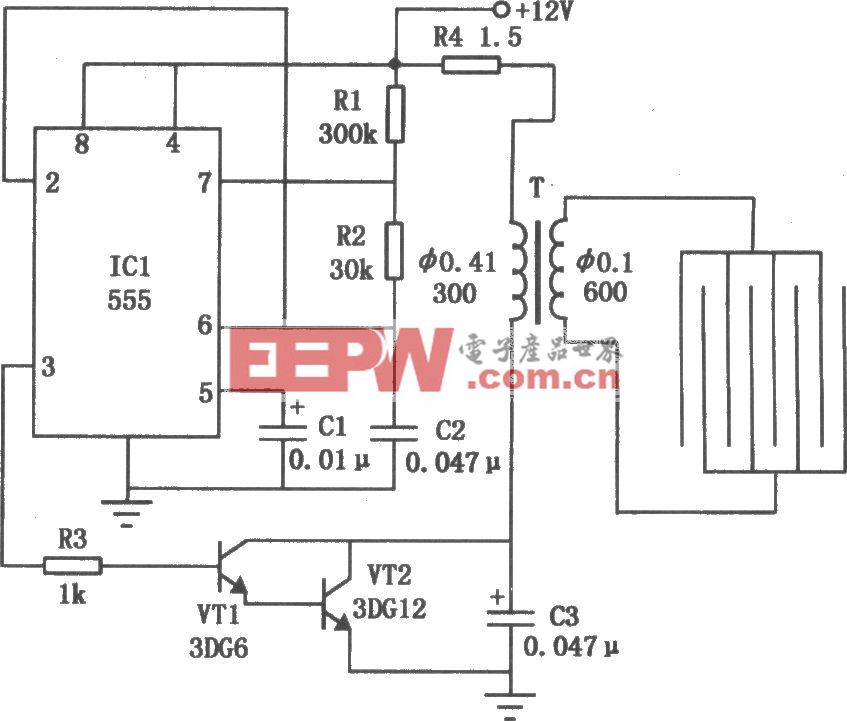

在这种情况下,用户必须在clka引脚上提供ds3、e3或者sts-1时钟。 用户必须至少向clka引脚提供三种频率(ds3、e3或者sts-1)中的一种。clad[3:0]位通知pll向这些引脚施加了何种频率。图1所示为ds316x、ds317x或者ds318x的clad单元。

图1. ds316x、ds317x和ds318x的clad单元 fm位(位于port.cr2中)用于选择由clad输出并施加给liu和发送器的时钟。clad具有很高的灵活性。可以接受三种时钟频率中的任何一种,并利用clad提供其余所需的频率。

也可以禁用clad,所有三个时钟由外部提供,使用clka、clkb和clkc引脚作为输入。当clad禁止时,必须分别向clka、clkb和clkc引脚施加ds3、e3和sts-1的三种参考频率。如果不会用到三种频率中的某些频率,则不必在对应的clad时钟引脚上施加该频率。

clad[3:0]控制位(位于gl.cr2寄存器)控制clad的工作模式,它确定各引脚的输入、输出特性,以及各个引脚所对应的时钟频率。详情请参考下面表1。

当clad[3:0] = 00xx时,pll电路被禁止, clka、clkb和clkc引脚上的输入时钟被用作内部liu的参考时钟。当clad[3:0] = (01xx或者10xx或者11xx)时,会有零、一或二个pll电路被使能,以产生所需的时钟,取决于clad[3:0]位、帧模式(fm[5:0])位和port.cr2中的线路模式控制位(lm[2:0])。

线路模式位选择主端口工作模式。如果不需要产生某个时钟来通过clad输出引脚输出或作为liu的参考时钟,那么用于产生该时钟的对应pll被禁止并处于掉电状态。

ds316x、ds317x和ds318x的clad配置寄存器

用于配置clad的两个寄存器如下所示。

寄存器名称:gl.cr2

寄存器说明:global control register 2

寄存器地址:004h

bit 3至0: clad io模式[3:0] (clad[3:0])。 这些位用于控制clad的时钟输入/输出引脚clka、clkb和clkc。这些寄存器位确定了采用哪个时钟从liu线路中恢复rx时钟。表1列出了详细情况。

bit 3至0: clad io模式[3:0] (clad[3:0])。 这些位用于控制clad的时钟输入/输出引脚clka、clkb和clkc。这些寄存器位确定了采用哪个时钟从liu线路中恢复rx时钟。表1列出了详细情况。

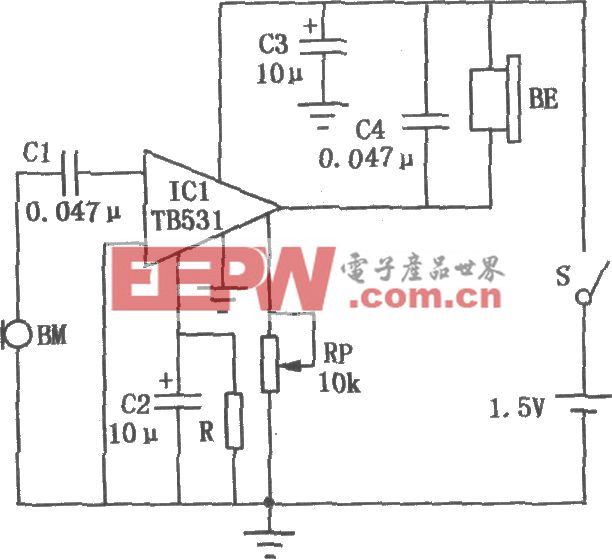

表1. clad输入/输出引脚编码详情

clad为接收liu提供参考时钟。接收liu根据用户选定(通过帧模式(fm)位)的模式选择时钟频率。fm位选择主成帧工作模式。如果通过port.cr3.cladc寄存器位选定,clad输出也可以用作发送时钟源。

clad为接收liu提供参考时钟。接收liu根据用户选定(通过帧模式(fm)位)的模式选择时钟频率。fm位选择主成帧工作模式。如果通过port.cr3.cladc寄存器位选定,clad输出也可以用作发送时钟源。

寄存器名称: port.cr3

寄存器说明:端口控制寄存器3

寄存器地址:(0, 2, 4, 6)44h

bit 3: clad发送时钟源控制(cladc)。 该位用于选择clad时钟作为内部发送时钟源。该位的功能还和其他控制位的设置有关。

bit 3: clad发送时钟源控制(cladc)。 该位用于选择clad时钟作为内部发送时钟源。该位的功能还和其他控制位的设置有关。

0 = 允许使用clad时钟做为发送时钟。

1 = 不采用clad时钟作为发送时钟(如果没有使能环回,由tclkin提供时钟源)。

配置ds31612、ds3168和ds3166的clad

在ds31612、ds3168和ds3166中,clad也由三个独立的pll单元构成。这些pll从参考时钟输入引脚(refclk)上的单一输入时钟产生多个时钟,用于传输时钟。为此,器件需要最多三种内部时钟,速率在ds3、e3和51.84。如果提供这三种频率中的一种作为参考时钟,另外两种可以被合成出来。ds31612、ds3168和ds3166支持77.76mhz和19.44mhz参考时钟频率(这一点与ds3161、ds3162、ds3163和ds3164不同),从它可以产生所有三种内部频率。内部时钟可作为一个备选的端口发送时钟。

当使用clk45、clk34和clk52引脚作为时钟输入时,还可以禁止clad,由外部提供所有三个时钟。当clad被禁止,而端口又被配置为使用clad时钟作为发送时钟时,被配置为ds3、e3和cc52的端口将分别使用clk45、clk34和clk52上的时钟。当clad被禁止时,clk45、clk34和clk52引脚上的时钟频率对于电路功能并无影响。但是,为了满足某种成帧类型的标准通信频率要求,这些频率通常分别为44.76mhz、34.368mhz和51.84mhz。

clad[5:0]控制位确定是否使能clad,refclk引脚上为何种参考频率,以及哪个clad时钟输入/输出引脚作为时钟输出引脚。

当clad[5:3] = 000、110或者111时,pll电路被禁止,clad时钟输入/输出引脚上的信号被用作输入时钟。当clad[5:3] = 001、010、011、100或者101时,零、一、二或三个pll电路被使能用来产生所需的时钟,取决于clad[2:0]位、帧模式位(fm[5:0])、clad控制位(cladc)、环路时间模式位(loopt)和全局8k参考选择位(g8krs[3:0])的设置。详情参见下面的表2和表3。

举例来讲,如果在一个设计中端口只工作在ds3速率下,那么clad[5:3]可以设置为= 001。refclk引脚上的ds3时钟被用于发送,没有pll电路被使能。

如果某个时钟频率不被任何单元使用,那么就可以关闭用来产生该时钟的pll。如果参考时钟与内部使用的某个时钟相同,那么就可使用refclk引脚上的时钟;用于产生该时钟的pll就可以关闭。

ds31612、ds3168和ds3166的clad配置寄存器

寄存器名称:gl.cr2

寄存器说明:全局控制寄存器2

寄存器地址:004h

bit 5至0: clad输入/输出模式[5:0] (clad[5:0])。 这些位控制着clad引脚refclk、clk45、clk34和clk52的工作模式。详见表2和表3。

bit 5至0: clad输入/输出模式[5:0] (clad[5:0])。 这些位控制着clad引脚refclk、clk45、clk34和clk52的工作模式。详见表2和表3。

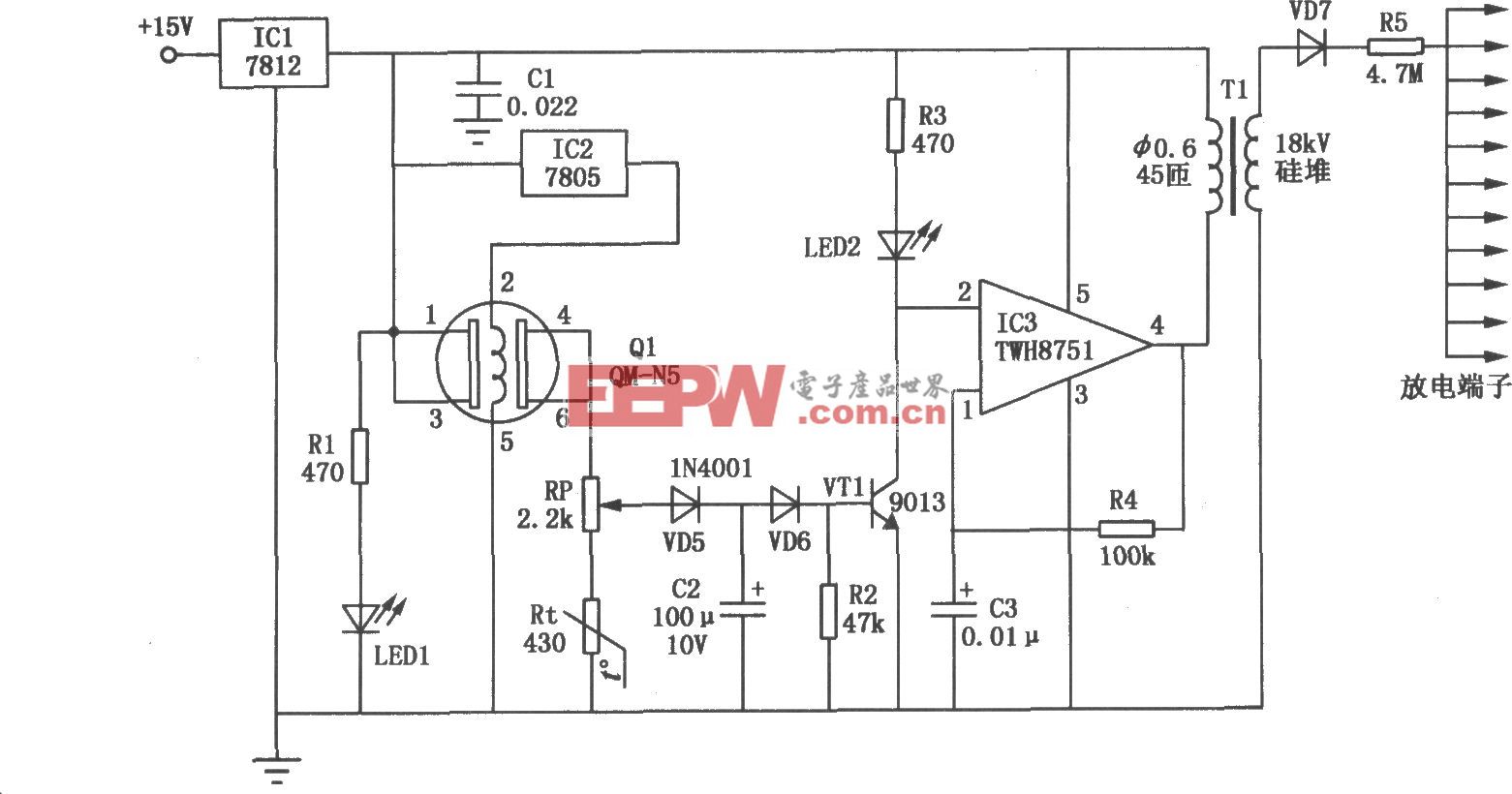

表2. clad时钟源设置

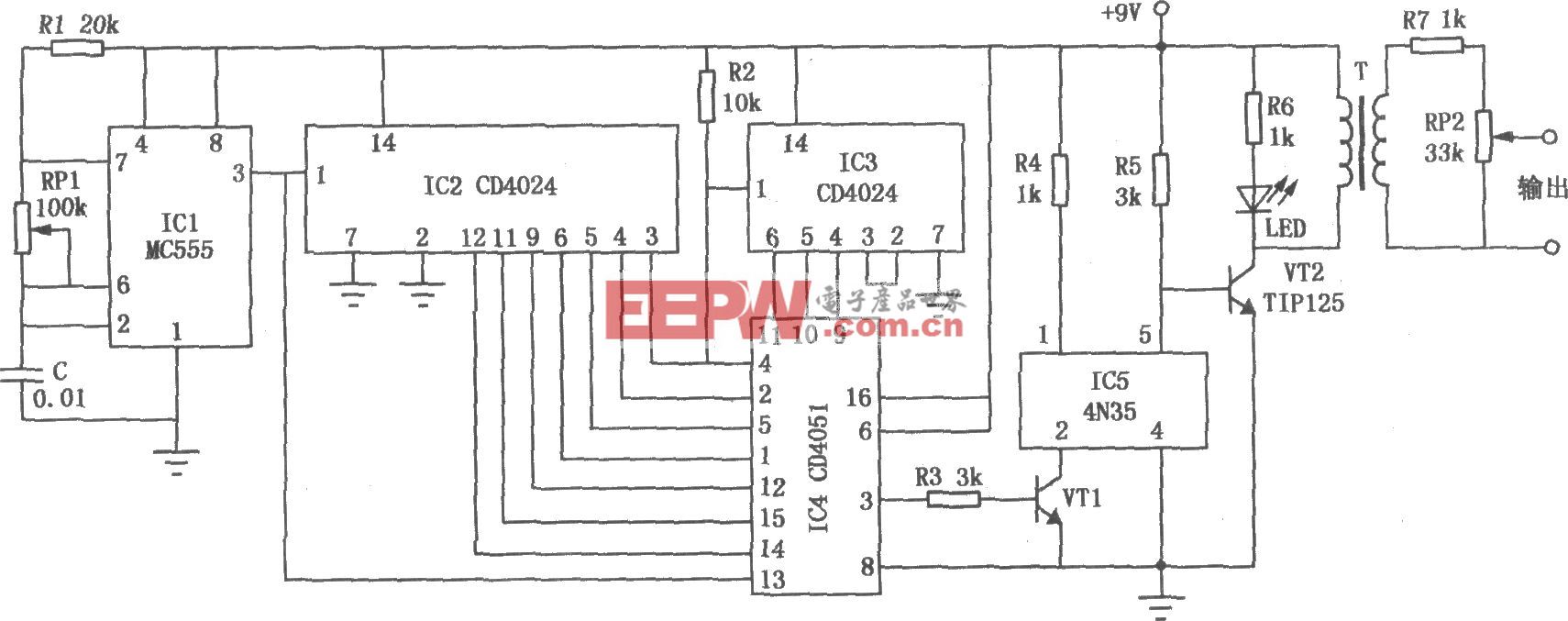

表3. clad时钟引脚输出设置

表3. clad时钟引脚输出设置  *注: 当clad[5:3] = 000、110或者111时,clk45、clk34和clk52为输入。

*注: 当clad[5:3] = 000、110或者111时,clk45、clk34和clk52为输入。

寄存器名称:port.cr3

寄存器说明:端口控制寄存器3

寄存器地址:(00,02,04,06,08,0a,0c,0e,10,12,14,16)44h

bit 3: clad发送时钟源控制(cladc)。 该位用于选择clad时钟作为内部发送时钟源。该位的功能与其他控制位的设置有关。

bit 3: clad发送时钟源控制(cladc)。 该位用于选择clad时钟作为内部发送时钟源。该位的功能与其他控制位的设置有关。

0 = 允许使用clad时钟做为发送时钟。

1 = 不采用clad时钟作为发送时钟(如果没有使能环回功能,时钟源为tclkin)。

结语

ds325x、ds316x、ds317x或者ds318x器件含有一个clad功能,可用于产生多种时钟作为liu参考时钟,或者供给用户应用作为发送时钟。关于dallas semiconductor器件中clad的工作如有进一步的问题,可通过电子邮件telecom.support@dalsemi.com (english only)或者致电usa 972-371-6555 (english only),联络dallas semiconductor的电信应用支持团队。

评论