时域时钟抖动分析(上)二

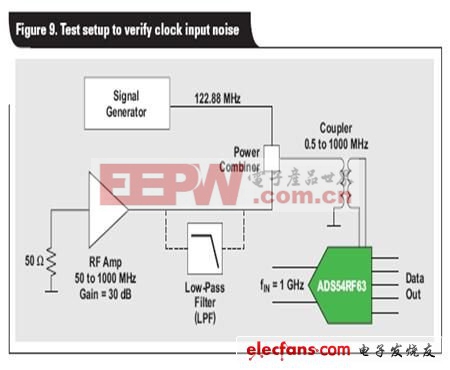

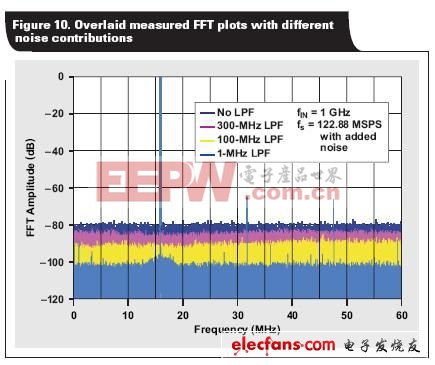

ADS54RF63 的时钟输入带宽为 ~2 GHz,但由于 RF 放大器和变压器都具有 ~1 GHz 的 3-dB带宽,因此有效 3-dB 时钟输入带宽被降低至 ~500 MHz。“表 2”所示测得 SNR 结果证实,就本装置而言,实际时钟输入带宽约为 500MHz。图 10 所示 FFT 对比图进一步证实了 RF 放大器的宽带噪声限制了噪声层,并降低了 SNR。

该实验表明,时钟相位噪声必需非常低或者带宽有限,较为理想的情况是通过一个很窄的带通滤波器。否则,由系统时钟带宽设定的整合上限会极大降低 ADC 的 SNR。

结论

本文介绍了如何准确地估算采样时钟抖动,以及如何计算正确的上下整合边界。“第 2 部分”将会介绍如何使用这种估算方法来推导 ADC 的 SNR,以及所得结果与实际测量结果的对比情况。

评论