基于PCB模拟设计的良好接地指导原则

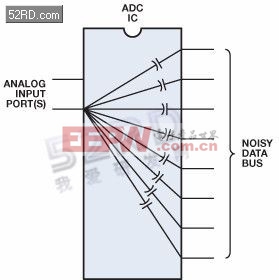

ADC输出与缓冲寄存器输入间的串联电阻(图4中标示为“R”)有助于将数字瞬态电流降至最低,这些电流可能影响转换器性能。电阻可将数字输出驱动器与缓冲寄存器输入的电容隔离开。此外,由串联电阻和缓冲寄存器输入电容构成的RC网络用作低通滤波器,以减缓快速边沿。

典型CMOS栅极与PCB走线和通孔结合在一起,将产生约10 pF的负载。如果无隔离电阻,1 V/ns的逻辑输出压摆率将产生10 mA的动态电流:

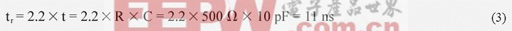

驱动10 pF的寄存器输入电容时,500 Ω串联电阻可将瞬态输出电流降至最低,并产生约11 ns的上升和下降时间:

由于TTL寄存器具有较高输入电容,可明显增加动态开关电流,因此应避免使用

缓冲寄存器和其他数字电路应接地并去耦至PC板的数字接地层。请注意,模拟与数字接地层间的任何噪声均可降低转换器数字接口上的噪声裕量。由于数字噪声抗扰度在数百或数千毫伏水平,因此一般不太可能有问题。模拟接地层噪声通常不高,但如果数字接地层上的噪声(相对于模拟接地层)超过数百毫伏,则应采取措施减小数字接地层阻抗,以将数字噪声裕量保持在可接受的水平。任何情况下,两个接地层之间的电压不得超过300 mV,否则IC可能受损。

最好提供针对模拟电路和数字电路的独立电源。模拟电源应当用于为转换器供电。如果转换器具有指定的数字电源引脚(VD),应采用独立模拟电源供电,或者如图6所示进行滤波。所有转换器电源引脚应去耦至模拟接地层,所有逻辑电路电源引脚应去耦至数字接地层,如图6所示。如果数字电源相对安静,则可以使用它为模拟电路供电,但要特别小心。

某些情况下,不可能将VD连接到模拟电源。一些高速IC可能采用+5 V电源为其模拟电路供电,而采用+3.3 V或更小电源为数字接口供电,以便与外部逻辑接口。这种情况下,IC的+3.3 V引脚应直接去耦至模拟接地层。另外建议将铁氧体磁珠与电源走线串联,以便将引脚连接到+3.3 V数字逻辑电源。

采样时钟产生电路应与模拟电路同样对待,也接地并深度去耦至模拟接地层。采样时钟上的相位

评论