衬底驱动轨至轨运算放大器设计

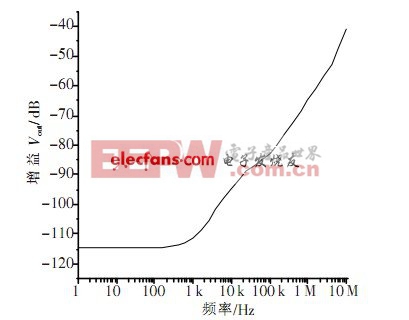

图4 运算放大器的幅频特性曲线

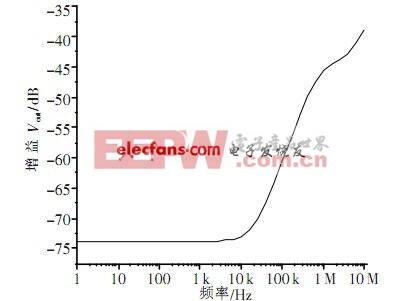

在运算放大器的两个输入端加相同的信号,做交流小信号分析,测出电路的共模电压增益如图5所示。在低频下,电路的共模增益为-114 dB,结合前面交流小信号分析的结果,可得出电路的共模抑制比为176.1 dB。图6为电压抑制比仿真曲线,低频时,电压抑制比约为-73.8 dB。

图5 共模电压增益

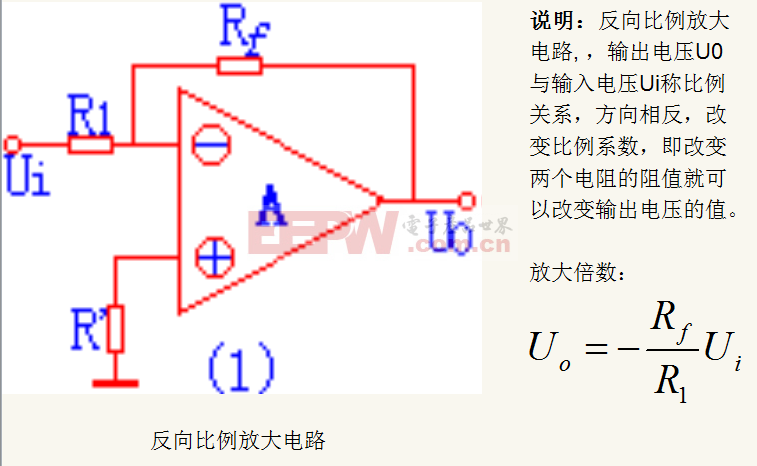

图6 电压抑制比仿真曲线

综上仿真结果表明,该衬底驱动运算放大器具有良好的性能。虽然运算放大器的频率带宽和线性度有所下降,但是却能有效避开阈值电压的限制,将电源电压降低到0.8 V,功耗为65.9 μW,同时实现了轨至轨的输入/输出电压范围。在传统的栅驱动轨至轨运算放大器信号通路中存在MOS管阈值电压的影响,因此限制了其在超低电源电压下的应用。

总结:本文通过采用衬底驱动互补差分对电路,有效降低了CMOS模拟集成电路对电源电压的要求,通过改进型前馈式AB类输出级来提高电压的增益,实现了超低压下运算放大器信号放大,获得了-0.36 V~0.39 V的共模输入范围和-0.39 V~0.395 V的输出电压范围。仿真得到该运算放大器具有良好的性能指标,能够有效地驱动阻性负载,且结构简单,适于低压低功耗模拟集成电路应用。

评论