数字频率合成精解:用DDS器件产生高质量波形

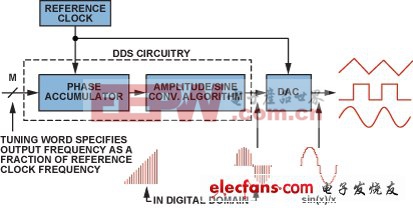

M为调谐字的分辨率(24至48位)

N为对应于相位累加器输出字最小增量相位变化的fC的脉冲数。

图2.典型的DDS架构和信号路径(带DAC)。

由于更改N会立即改变输出相位和频率,因此,系统自身具有相位连续,特点,这是许多应用的关键属性之一。无需环路建立时间,这与模拟系统不同,如锁相环 (PLL)。

DAC通常为一个高性能电路,专门针对DDS内核(相位累加器和相幅转换器)而设计。多数情况下,结果形成的器件(通常为单芯片)一般称为纯DDS或C-DDS。

实际的DDS器件一般集成多个寄存器,以实现不同的频率和相位调制方案。如相位寄存器,其存储的相位内容被加在相位累加器的输出相位上。这样,可以对应于一个相位调谐字延迟输出正弦波的相位。对于通信系统相位调制应用,这非常有用。加法器电路的分辨率决定着相位调谐字的位数,因此,也决定着延迟的分辨率。

在单个器件上集成一个DDS引擎和一个DAC既有优点也有缺点,但是,无论集成与否,都需要一个DAC来产生纯度超高的高品质模拟信号。DAC将数字正弦输出转换为一个模拟正弦波,可能是单端,也可能是差分。一些关键要求是低相位噪声、优秀的宽带(WB)和窄带(NB)无杂散动态范围 (SFDR)以及低功耗。如果是外部器件,则DAC必须足够快以处理信号,因此,内置并行端口的器件非常常见。

DDS与其他解决方案

其他产生频率的方法包括模拟锁相环(PLL),时钟发生器和利用FPGA对DAC的输出进行动态编程。通过考察频谱性能和功耗,可以对这些技术进行简单的比较,表1以定性方式展示了比较结果

表1.DDS与竞争技术——高级比较

锁相环是一种反馈环路,其组成部分为:一个相位比较器, 一个除法器和一个压控制振荡器 (VCO)。 相位比较器将基准频率与输出频率(通常是输出频率的N)分频)进行比较。相位比较器产生的误差电压用于调节VCO,从而输出频率。当环路建立后,输出将在频率和/或相位上与参考频率保持一种精确的关系。PLL长期以来一直被认为是在特定频带范围内要求高保真度和稳定信号的低相位噪声和高无杂散动态范围 (SFDR) 应用的理想选择。

由于PLL无法精确、快速地调谐频率输出和波形,而且响应较慢,这限制了它们对于快速跳频和部分频移键控和相移键控应用的适用性。

其他方案,包括集成DDS引擎的现场可编程门阵列 (FPGAs) ——配合现成DAC以合成输出正弦波——虽然可以解决PLL的跳频问题,但也存在自身的缺陷。主要系统缺陷包括较高的工作和接口功耗要求、成本较高、尺寸较大,而且系统开发人员还须考虑额外的软件、硬件和存储器问题。例如,利用现代FPGA中的DDS引擎选项,要产生动态范围为60 dB的10 MHz输出信号,需要多达72 kB的存储器空间。另外,设计师需要接受并熟悉细微权衡和DDS内核的架构。。

评论