∑-△ADC的降采样滤波器方案

4.1.4 时钟的处理

系统用到了多个分频时钟,为了方便后面布局布线做时钟树,本设计采用计数器产生使能信号进行分频。

4.1.5 Design Compiler综合

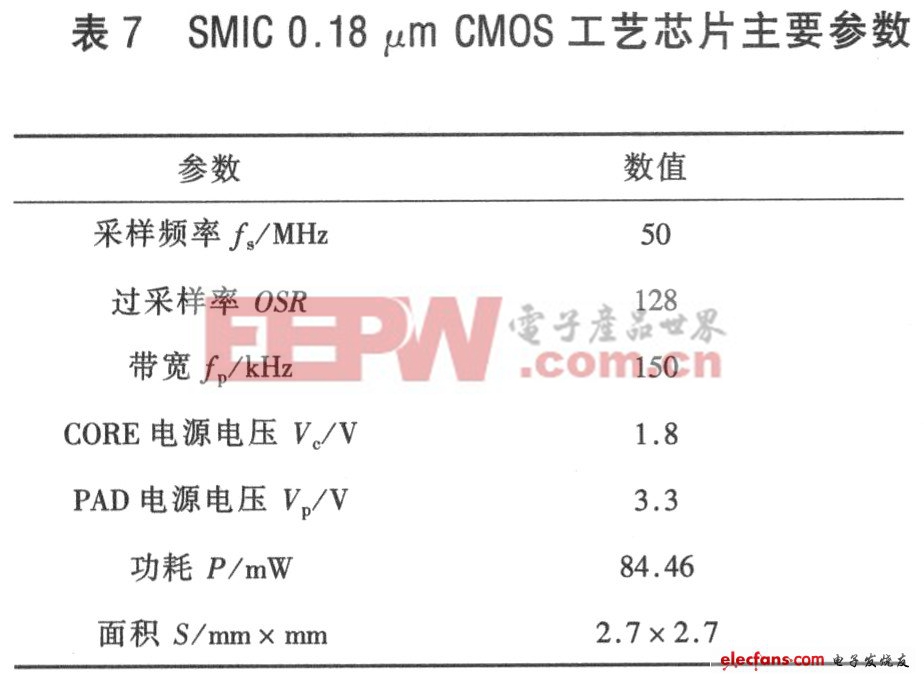

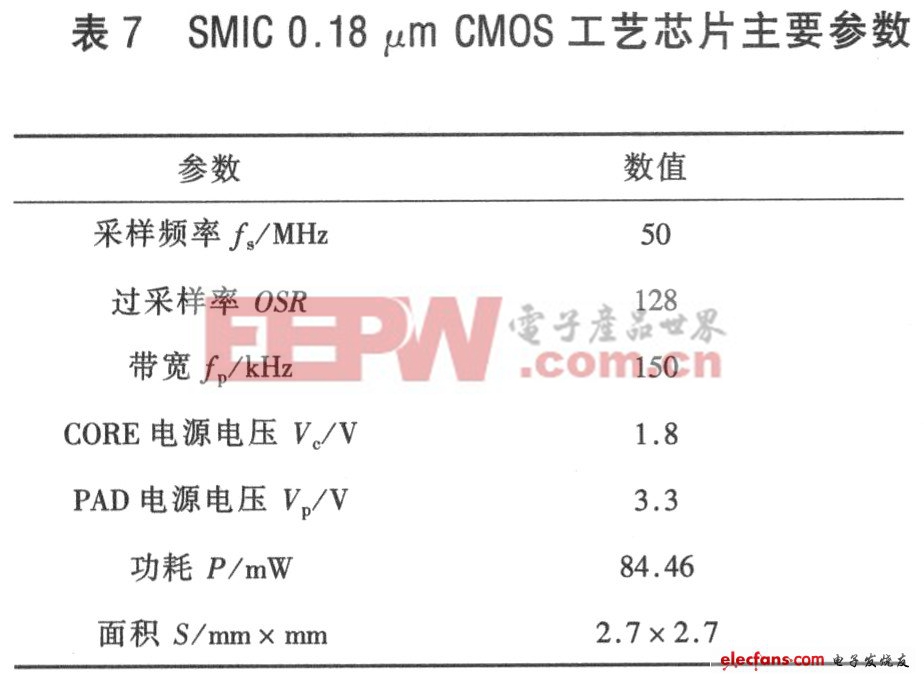

本设计采用SMIC 0.18μm CMOS工艺库,将编写的Verilog代码用Synopsy的Design Compiler综合,通过加上适当的约束条件反复优化,最终得到综合结果。综合结果通过Synopsys VCS仿真验证。

4.2 版图设计

本设计采用Cadence Encounter对综合后的滤波器的门级网表进行布局布线,图5是完成布局布线后的版图。芯片主要参数如表7所示。

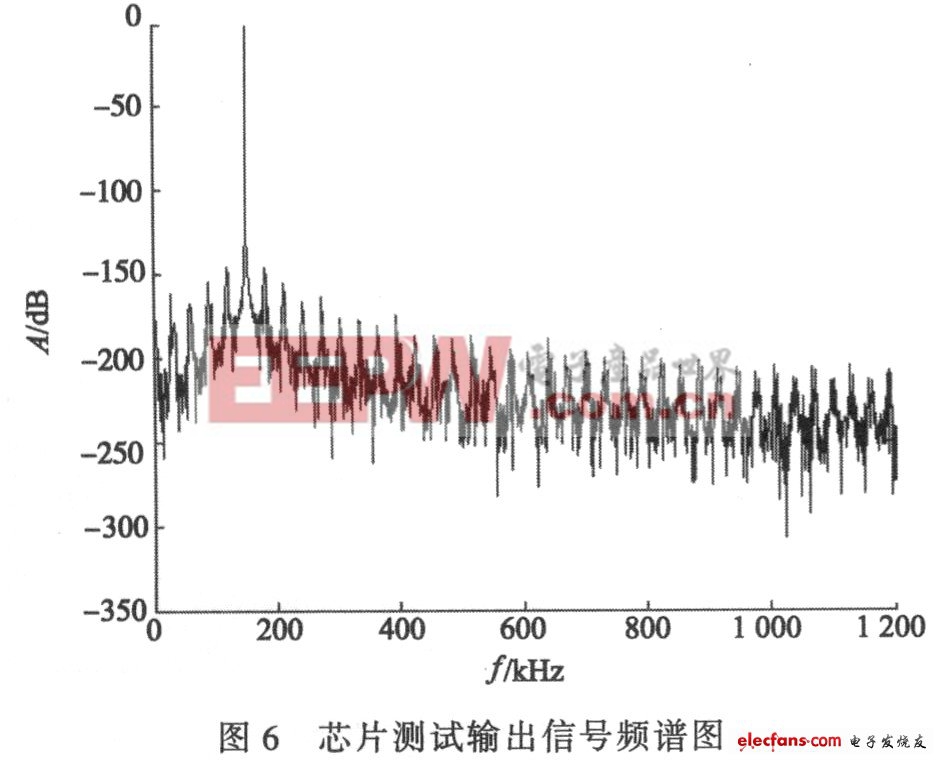

5 芯片测试

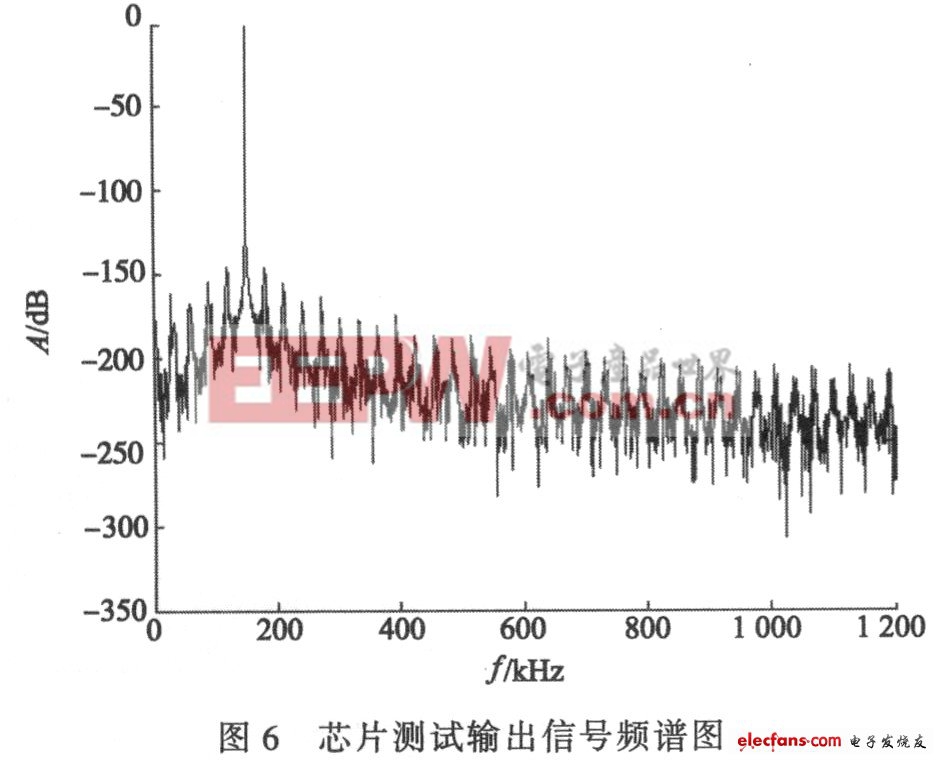

在模拟三阶CRFB结构的∑-△调制器输入的情况下,通过逻辑分析仪采集输入为150 kHz正弦信号的输出数据,并由计算得到的频谱如图6所示,信号与噪声加失真比(SINAD)大于86 dB,满足性能指标要求。

6 结论

通过Synopsy的Design Compiler进行电路综合和Cadence Encounter进行布局布线,采用SMIC 0.18μm CMOS工艺实现。系统仿真和芯片测试结果表明,性能满足设计指标要求。

电源滤波器相关文章:电源滤波器原理

评论