复位设计中的结构性缺陷及解决方案(二)

4. 解决方案

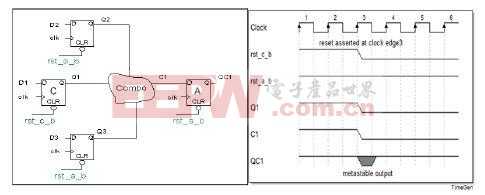

可用以下方式编写RTL代码,以避免同步链的组合逻辑。

always @(posedge clk )

if(!sync_rst_b) begin

sync1 = 1‘b0;

end

else begin

sync1 = async_in; sync2 = sync1

end

在上面的代码中,对sync2触发器不使用复位,因此在同步链中不会实现组合信元。然而,需要注意sync2需要一个额外的周期才能复位,这不应导致设计出现任何问题。

冗余复位同步器引起的问题

1. 问题

在使用多个异步时钟的设计中,设计人员需要确保在目标寄存器使用的时钟方面,异步复位的同步去断言,否则可能导致目标触发器发生时序违反,从而产生亚稳态。复位同步器被用来复位去断言,与目标时钟域同步。然而,只有在系统复位去断言过程中有目标时钟时才会发生复位去断言时序违反。如果在复位去断言时没有时钟,那么便不会有任何时序违反。因此,在设计多时钟域模块时,设计人员可以让编译时间选项绕过该模块中的那些复位同步器,并让系统集成商根据对该模块的时钟可用性决定是否需要使用复位同步器。

此外,如果系统时钟和异步时钟比非常高,冗余同步器甚至会造成设计功能性问题。下面描述了这个问题。

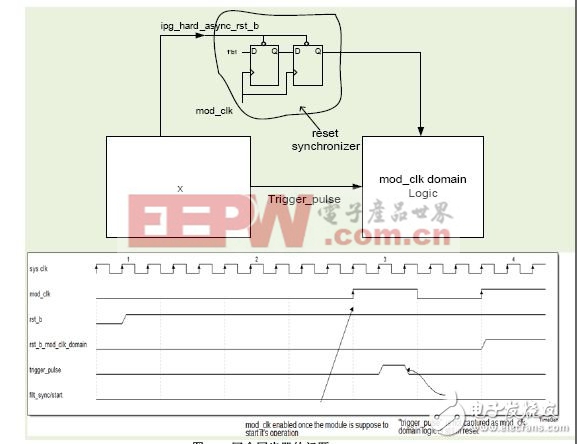

图12:冗余同步器的问题

在上面的设计中,去断言与sys clk同步的系统复位被馈送到(mod_clk域)的复位同步器,然后在mod_clk域逻辑中使用该复位。让我们假定sys clk : mod_clk的时钟频率比大于6:1.默认不启用mod_clk,以节省动态功率。当用户想要启用mod_clk域逻辑的功能时,便启用该时钟。在启用了该时钟后,有两个mod_clk周期的延迟,其中,由于复位同步器导致整个mod_clk域逻辑都处于复位状态。在该阶段,如果一些数据交易从sys clk域开始,将在mod_clk域丢失。

2. 解决方案

虽然这不是大问题,但有时会在客户一端造成混淆,因为该延迟对客户不可见。 因此消除混淆的更好的方式是:

* 如果在全局复位去

评论