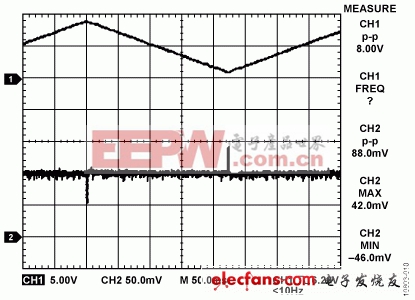

接至AVDD的电容可用于抵消滤波器输出端因压摆时间过快而导致的峰值电压增加。然而,选择此值时必须小心,因为它会影响“确定外部元件值”部分讨论的低通滤波器截止频率。图10显示了压摆率控制设置改为SR时钟= 5、SR阶跃= 2且C1电容值保持4.7 nF不变的结果。这样,转换时间就会在240 ms左右。滤波器输出端的峰值幅度可通过增加C1值、配置更慢的压摆率或通过两者的组合来进一步降低。

图10. AD5422输出(通道1)和HART滤波器输出(通道2),SR时钟= 5,SR阶跃= 2,C1 = 4.7 nF,C2 = NC

评论