如何设计一个放大电路(2)噪声

放大系统降噪的核心思路是 “抑制内部固有噪声 + 阻断外部干扰噪声”,需结合元器件选型、电路拓扑、布线屏蔽等多维度措施,以下是结构化、可直接落地的解决方案:

一、 抑制内部固有噪声(器件与电路层面)

内部噪声由放大器件(晶体管、运放)、无源元件(电阻)本身产生,是系统的本底噪声,决定了降噪的下限。

元器件选型优化

由于经典的模电教材、文档往往都是由ADI、TI这样芯片设计公司的专家写的,他们更多的视角是器件本身。所以大量的文档篇幅都是描述器件本身的评估。

估算的方法很多教材和文档都有描述,我这里就先不展开。我们后续内容再展开。

一个不可回避的事实就是:我们实际设计出来的电路的噪声远远大于评估噪声。这是什么原因呢?

因为除了器件自身的噪声之外,跟我们的设计有很大的关系。

电路拓扑与增益分配优化

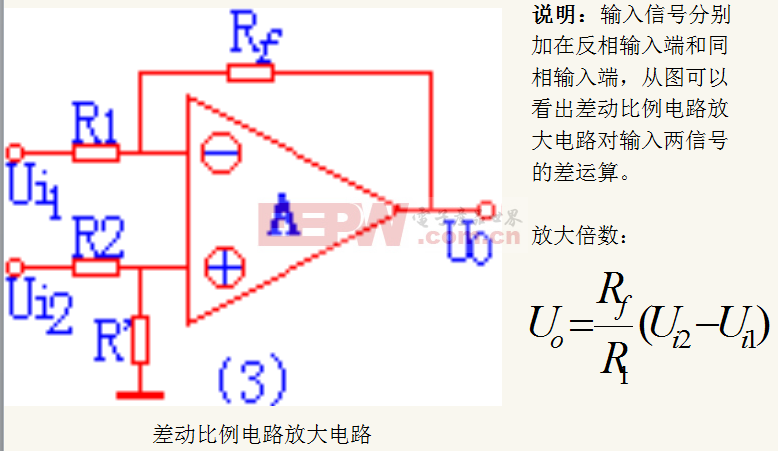

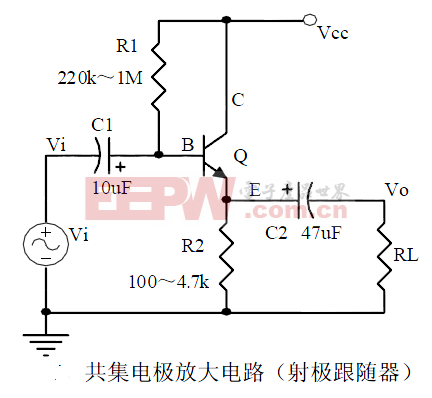

晶体管电路: 射极跟随器(共集电极)噪声系数低于共射放大;共射放大可加射极电阻负反馈降低噪声。

运放电路: 同相放大的噪声增益更低(噪声增益 Gn=1+R1Rf ),优于反相放大(噪声增益等于信号增益)。

决定(噪声系数级联公式: Ftotal≈F1+G1F2−1 ),前级要 低噪声 + 适度增益(如 10~20 倍),后级负责提升总增益,不贡献额外噪声。

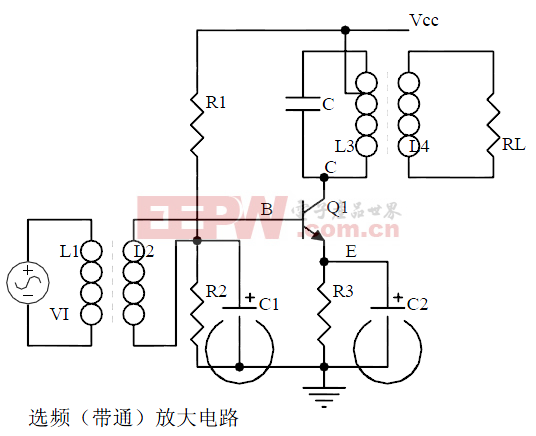

Pn∝Δf ),用 RC 低通或有源滤波器,将带宽限制在 信号最高频率的 1.2~1.5 倍,滤除带外噪声。

反馈网络降噪反馈电阻的噪声会被放大,需选低噪电阻,且阻值不宜过大;可在反馈电阻并联小电容,形成极点抑制高频噪声。

二、 阻断外部干扰噪声(系统与布线层面)

外部噪声是放大系统的主要干扰来源,包括电源纹波、电磁干扰(EMI)、接地噪声等,需通过 “隔离 + 屏蔽 + 滤波” 切断干扰路径。

1、电源噪声抑制

1.1 选择PSSR更好的运放

运放的电源抑制比(PSSR,Power Supply Rejection Ratio)是衡量其抑制电源电压波动对输出影响能力的核心指标,数值越高(单位为 dB),电源噪声抑制效果越好。高 PSSR 运放的设计核心是切断或衰减电源噪声向输出端的耦合路径,主要通过电路架构优化、模块设计改进、工艺选型、频率补偿四个维度实现,具体原理如下:

一、 输入级电路架构优化:阻断噪声耦合的第一道防线

运放的电源噪声主要通过输入级偏置电路和有源器件的衬底 / 寄生电容耦合到信号通路,高 PSSR 运放的输入级设计重点是降低这种耦合效率。

共栅管的输出阻抗极高,大幅降低了电源电压波动对差分对漏极电压的影响;

同时抑制了 密勒效应,减少寄生电容带来的高频噪声耦合。

采用共源共栅(Cascode)差分输入结构

普通差分输入级的晶体管直接连接电源,电源电压波动会直接改变晶体管的工作点(如漏极电流、跨导),进而影响差分对的输出。共源共栅结构在差分对上方叠加一级共栅管,相当于给输入级增加了一个 “隔离层”:

稳定的偏置电路设计输入级的偏置电流决定了差分对的跨导和工作稳定性,高 PSSR 运放普遍采用带隙基准(Bandgap Reference)或电流镜偏置,而非简单的电阻分压偏置:

电流镜采用匹配性极佳的晶体管对,抵消电源波动对偏置电流的影响,避免偏置变化导致的信号失真。

带隙基准的输出电流 / 电压几乎不受电源电压波动影响(电源抑制比可达 100dB 以上),确保差分对的偏置电流稳定;

差分输入的对称设计对于双电源供电的运放,采用完全对称的差分输入级,让正负电源的噪声在差分对中相互抵消。例如,正负电源的波动幅度相同时,差分对的两个输入端受到的影响一致,最终输出的差值为零,实现噪声抵消。

1.2 增益级设计:提升增益间接增强电源抑制能力

PSSR 与运放的开环增益直接相关,核心公式为:

在相同的电源噪声(ΔVCC)下,开环增益越高,输出端的噪声(ΔVOUT)越小,PSSR 数值越大。高 PSSR 运放的增益级设计主要有两个方向:

1.3 集成内部稳压 / 去耦模块:从源头过滤电源噪声

部分高性能高 PSSR 运放(如精密运放、低噪声运放)会在芯片内部集成微型 LDO(低压差稳压器)或去耦电容,直接对外部输入的电源进行预处理:

1.4 工艺与寄生参数优化:减少非理想因素的影响

芯片制造工艺和版图设计的非理想因素(如衬底耦合、寄生电容 / 电感)会显著降低运放的高频 PSSR,高 PSSR 运放的工艺优化重点如下:

1.5 频率补偿设计:保证宽频段的 PSSR 稳定性

PSSR 是频率相关参数:低频段运放开环增益高,PSSR 数值大;高频段开环增益下降,PSSR 会随之降低。高 PSSR 运放的频率补偿设计目标是拓宽高 PSSR 的频率范围:

电源引脚和信号引脚分开布局,避免电源噪声通过布线的寄生电容耦合到信号通路;

差分对晶体管采用 匹配性版图设计(如共质心布局),降低工艺偏差导致的电源噪声抑制能力下降;

增加电源地线的宽度,降低地线阻抗,减少电源波动的幅度。

采用 米勒补偿或超前 - 滞后补偿,在保证运放相位裕度的前提下,优化开环增益的频率响应,避免在关键频段(如 10kHz-1MHz)出现 PSSR 的 “低谷”;

增加高频去耦网络,针对开关电源等高频噪声源,提升特定频段的噪声抑制能力。

采用 SOI(绝缘体上硅)工艺

传统体硅工艺中,晶体管的衬底直接接地,电源噪声会通过衬底的寄生电阻 / 电容耦合到有源器件。SOI 工艺采用绝缘层将衬底与器件隔离,彻底切断衬底耦合路径,大幅提升高频 PSSR(尤其是 1MHz 以上频段)。

优化版图布局与布线

内部 LDO 稳压

LDO 的作用是将外部波动的电源电压转换为稳定的直流电压,再供给运放的核心模块(输入级、增益级)。外部电源的噪声会被 LDO 的反馈环路抑制,核心模块相当于工作在 “干净” 的电源下,从源头消除噪声耦合。

片内集成去耦电容

在电源引脚与地之间集成 pF 级的片内去耦电容,用于滤除高频电源噪声(如开关电源的纹波)。相比外部去耦电容,片内电容的寄生电感更小,高频滤波效果更好,能有效抑制 MHz 级别的电源噪声。

多级增益级联 + 折叠式共源共栅结构单级增益级的增益有限(通常 30-40dB),高 PSSR 运放采用2-3 级增益级联,并在每一级采用折叠式共源共栅结构,将开环增益提升至 80-120dB,大幅提升电源噪声抑制能力。

避免增益级直接耦合电源增益级的晶体管采用电流源负载替代传统的电阻负载,电流源的输出阻抗远高于电阻,不仅能提升增益,还能降低电源波动对负载电压的影响,进一步阻断噪声通路。

2、分级滤波去耦

每级放大电路的电源引脚旁并联 0.1μF 陶瓷电容 + 10μF 电解电容

,陶瓷电容滤高频噪声,电解电容滤低频纹波;多级放大的各级电源分开滤波,避免串扰。并且采用RC做电源滤波。

优选低纹波供电:用线性稳压器(LDO) 代替开关电源(开关电源高频纹波大);若必须用开关电源,需加 EMI 滤波器和 LC 滤波电路(如 10μH 电感 + 100μF 电容)。

输入信号线 短、粗、直,远离功率线、数字信号线(如 MCU 的 IO 线),间距大于 3 倍线宽。

敏感信号线(如前级输入线)采用 屏蔽线,屏蔽层单端接地(两端接地会形成接地环路)。

前放是易受干扰电路,我们要考虑其他电路对他的干扰。即需要考虑容性耦合,也需要考虑感性耦合。基本分析的过程跟我们之前内容分析开关电源的环路部分是一个原理。

接地策略:低频放大(10MHz)用多点接地**,缩短接地路径。

放大系统的 前级输入部分放入金属屏蔽盒(如铝盒),屏蔽盒可靠接地,阻挡外部电磁辐射(如电机、继电器、射频信号)。

若外部有强干扰源(如扫地机器人的电机、无人机的电调),需对干扰源单独屏蔽,并做好接地。

隔离技术当存在地电位差或强干扰时,采用光电隔离或磁隔离放大器,将输入信号与放大电路完全隔离,切断干扰传导路径。

温度控制:电阻热噪声、晶体管噪声随温度升高而增大,精密放大系统需远离热源(如功率管、电源模块),必要时加散热片或恒温措施。

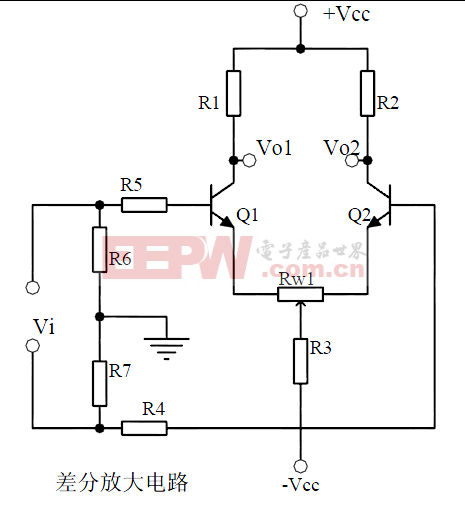

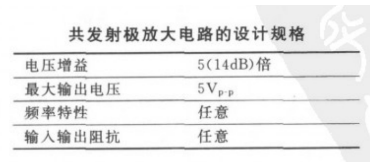

差分放大抑制共模噪声:对于存在共模干扰的场景(如长线传输信号),用差分放大电路(如仪用放大器 AD620),利用共模抑制比(CMRR)抑制共模噪声。

评论