面向Home Bus系统的电感选型指南

规则1:两个电感应尽可能相互靠近放置,以减少磁通泄漏。

当两个电感“耦合”时,电感对的总电感大于L1 + L2(L1和L2的串联组合)。总电感LTOTAL = L1 + L2 + 2M,其中M是L1和L2磁耦合所产生的互感。互感M = k x √(L1xL2),其中k是介于0和1之间的耦合系数。k=1表示磁通漏泄为零,L1和L2之间100%磁耦合。图8(C)中的红线表示两个电感之间的磁耦合;两个电感位置越近,耦合越理想,泄漏越小,因此互感M越大。

耦合系数k = 1时,如图8(A)所示配置的两个8.3mH电感的最终差模电感为L1 + L2 + 2k x √(L1 x L2) = 33.2mH。实际上,耦合系数k始终小于1。当这两个电感相距1mm时,测得的差模电感为25.8mH。电感减小是由磁通泄漏造成的。互感M = 0.5 x (25.8mH - 8.3mH x 2) = 4.6mH,表明耦合系数k = M/√(L1 x L2) = 4.6mH/8.3mH = 0.55。

当这两个电感相距1cm时,最终差模电感进一步减小,实测值为19.3mH。耦合系数降至0.33。

当这两个电感相距10cm时,测得的差模电感为16.6mH,与两个独立电感串联连接且无任何磁耦合的情况相同。这意味着磁耦合太弱,无法产生任何有意义的互感。

规则2:以差模配置将其配对。放置两个单独电感,使得在差模信号通过时,磁通沿相同方向产生。

当耦合对采用共模配置时,两个电感的磁通在差模信号通过时,沿相同方向产生并相互抵消,如图9所示。总电感LTOTAL减小,小于L1和L2的串联组合。

图9 (A)共模连接,(B)PCB上,(C)差模信号通过时的磁场

当两个电感采用差模配置(如图8(B)所示)且相距1cm时,测得的差模电感为20.3mH,大于两个独立电感的串联组合16.6mH。磁通相加,使得最终耦合电感更大。

当两个电感采用共模配置(如图9(B)所示)且相距1cm时,测得的差模电感为14.7mH,小于16.6mH。磁通相互抵消,使得最终耦合的差模电感减小。

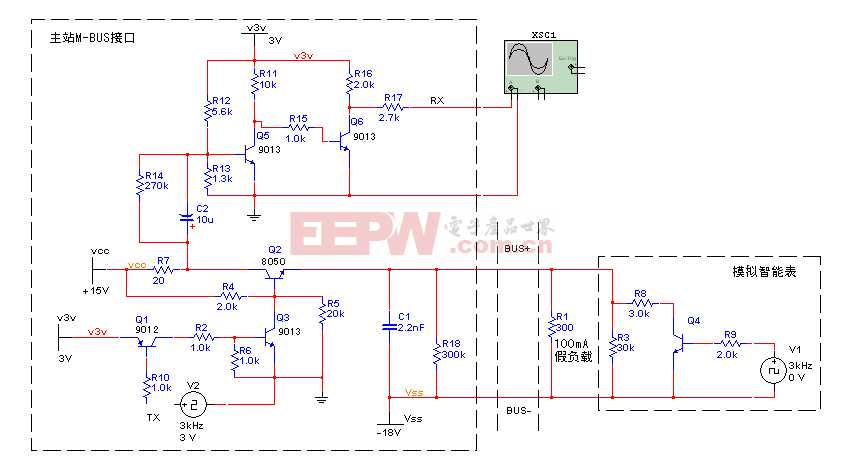

在图10和图11中,两个Home Bus节点以50kbps的速率进行通信,使用两个独立电感创建“交流阻断”电感对。从表2可知,在50kbps数据速率下,所需的总线总电感为0.8mH。图10显示,当使用两个390μH电感来实现780μH的总电感(小于所需的最小总线电感)时,接收器波形发生失真。电感对负载200mA电流,这进一步降低了总线上的总有效电感。图11显示,当电感对由两个3.9mH电感构成以实现大于所需最小值的总线电感时,相同工作条件下的总线波形干净无失真。

图10 50kbps总线波形,使用两个390µH独立电感作为“交流阻断”电感对

图11 50kbps总线波形,使用两个3.9mH独立电感作为“交流阻断”电感对

使用变压器

电力变压器用于在初级侧和次级侧之间升压或降压。在Home Bus应用中使用变压器时,应注意以下要求:

确保匝数比为1:1。大多数变压器的匝数比通常不是1:1。初级侧和次级侧通常具有不同的交流电压。

测量差模电感,因为数据手册中往往不会给出线圈电感。

变压器通常尺寸庞大,需要占据巨大的空间。

使用共模扼流圈

共模扼流圈用于滤除共模噪声。大多数共模扼流圈不适合Home Bus应用,原因如下:

差模电感比共模电感小得多。

共模扼流圈的额定电流相对较小,其典型工作频率通常远高于Home Bus应用使用的数据速率。

测量差模电感

大多数电感的数据手册未提供Home Bus应用所用数据速率和偏置电流条件下的差模电感信息。通常,鉴定所选电感对的最简单方法是使用LCR表测定其特性。在应用的数据速率和偏置电流下测量差模电感和相位时,应注意以下几点:

理想电感具有+90°相位,意味着其电流落后于其电压90°。

当电感磁芯饱和时,电感值会迅速下降。数据手册中有时会给出滚降率。

每个电感都有一个自谐振频率,该值通常随直流偏置电流而变化。

使用LCR表是标定所选电感的最简单方法。图12显示了使用LCR表测量差模电感的典型设置。表3展示了在实验室中使用Instek LCR-6300仪表进行测量的四个例子,并列出了它们在200kbps数据速率和200mA负载电流的Home Bus应用中的性能。

图12 使用LCR表测量差模电感

表3 使用LCR表进行特性分析和波形测量

Wurth差分电感 产品型号750318652 | Sumida差分电感 产品型号T92272 |

L = 352μH θ = 78° Q = 4.7 | L = 408μH θ = 83° Q = 8.2 |

Wurth耦合电感 产品型号744870471 | Wurth电力线扼流圈 产品型号7446323004 |

L = 1715μH θ = 87° Q = 26 | L = 22μH θ = 88° Q = 33.2 |

根据表2,200kbps条件下所需的总线最小总电感为200μH。Wurth共模电力线扼流圈(产品型号7446323004)无法提供所需的最小差模电感,因此总线波形发生失真。

设计示例

示例1:57.6kbps的双节点网络

考虑一个以57.6kbps数据速率运行的双节点Home Bus网络,如图3所示。图13为简化的等效模型。供电节点通过“交流阻断”电感L1向总线供应100mA电流,而MAX22088通过其集成的“有源电感”从总线获取电力。在此示例中,元件针对57.6kbps数据速率进行了优化,选择Wurth Electronics, Inc. 的100mH耦合电感(产品型号750318652)作为“交流阻断”电感L1。

图13 双节点网络等效模型

为了确定此耦合电感能否用于该应用,计算总线上的总阻抗ZBUS = ZL1 || (ZC1+ RIO1) || (ZC1 + RIO1) || ZLAC || (ZC2 + REQV + ZC2),其中:

L1 = 138mH(20kHz、100mA偏置电流条件下,来自基准特性测试)

LAC = 22.4mH(使用MAX22088数据手册中的公式)

静态端接电阻RTRM2 = 1kΩ

MAX22288 AIO/BIO输入阻抗RIO1 = 30kΩ(典型值)

MAX22088 AIO/BIO输入阻抗RIO2 = 10kΩ(典型值)

REQV = 952Ω,由下式得出:1/REQV = 1/(2 x RIO2) + 1/RTRM2

耦合电容 = 2.2μF

数据速率 = 57.6kbps,或f0 = 28.8kHz

所以,

ZL1 = 2π x f0 x L1 = 25kΩ

ZLAC = 2π x f0 x LAC = 4kΩ

ZC1 = ZC2 = 1/(2π x f0 x 2.2μF) = 2.5Ω

ZC1 + RIO1 = 30kΩ

ZC2 + REQV + ZC2 = 957Ω

因此,ZBUS = ZL1 || (ZC1+RIO1) || (ZC1 + RIO1) || ZLAC || (ZC2 + REQV + ZC2) = 25kΩ || 30kΩ || 30kΩ|| 4kΩ || 957Ω = 713Ω,大于所需的最小总线端接电阻100Ω。

MAX22088和MAX22888评估套件均使用了该Wurth耦合电感,它支持57.6kbps的Home Bus应用。

示例2:200kbps的8节点网络

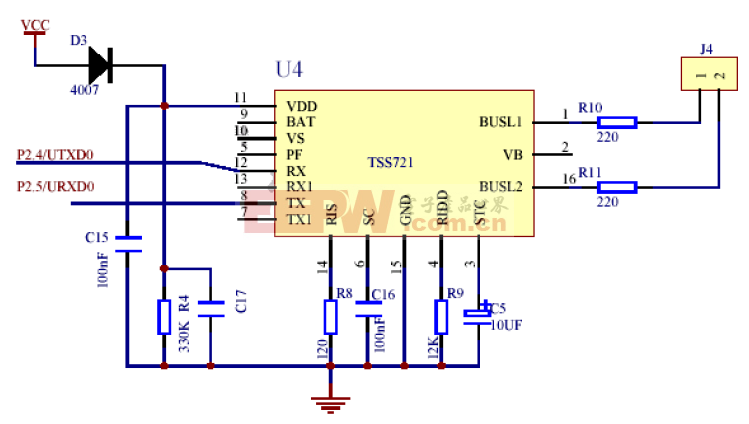

在此示例中,考虑一个以200kbps速率运行的8节点Home Bus系统,如图14所示。L1是供电节点中的“交流阻断”电感,为总线提供总计250mA的电流。我们需要确定是否能够使用Wurth Electronics, Inc.的耦合电感(产品型号744851102)。

图14 简化的8节点Home Bus系统

总线上的总阻抗ZBUS = ZNODE1 || ZNODE2 || ZNODE3 || ZNODE4 || ZNODE5 || ZNODE6 || ZNODE7 || ZNODE8,其中:

ZNODE1是节点1(供电节点)的总阻抗。

ZNODE2至ZNODE6是节点2至6(纯数据节点)的总阻抗。

ZNODE7和ZNODE8是节点7和8(受电节点)的总阻抗。

图15 (A)节点1(供电节点)、(B)节点2至6(纯数据节点)和(C)节点7至8(受电节点)的等效电路

考虑供电节点及其等效电路,如图15(A)所示,ZNODE1 = ZL1 || (ZC1 + REQV1 + ZC1),其中:

L1 = 358μH(100kHz、250mA偏置电流条件下,来自基准特性测试)

静态端接电阻RTRM1 = 1kΩ

MAX22288 AIO/BIO输入阻抗RIO1 = 30kΩ(典型值)

REQV1 = 983.6Ω,由下式得出:1/REQV1 = 1/(2*RIO1) + 1/RTRM1

耦合电容 = 1μF

数据速率 = 200kbps,或f0 = 100kHz

所以,

ZL1 = 2π x f0 x L1 = 225Ω

ZC1 = 1/(2π x f0 x 1μF) = 1.6Ω

ZC1 + REQV1 + ZC1 = 987Ω

因此,ZNODE1 = 225Ω || 987Ω = 183Ω。

考虑纯数据节点及其等效电路,如图15(B)所示,ZNODE2-6 = (ZC1 + RIO1) || (ZC1 + RIO1),其中:

MAX22288 AIO/BIO输入阻抗RIO1 = 30kΩ(典型值)

ZC1 = 1/(2π x f0 x 1μF) = 1.6Ω

因此,ZNODE2-6 = (30kΩ + 1.6Ω) || (30kΩ + 1.6Ω) = 15kΩ。

考虑受电节点及其等效电路,如图15(C)所示,ZNODE7-8 = ZLAC || (ZC2 + RIO2) || (ZC2 + RIO2),其中:

LAC7 = 35mH(50mA负载电流下,使用MAX22088数据手册中的公式)

LAC8 = 16mH(200mA负载电流下,使用MAX22088数据手册中的公式)

MAX22088 AIO/BIO输入阻抗RIO1 = 10kΩ(典型值)

所以,

ZLAC7 = 2π x f0 x LAC7 = 22kΩ

ZLAC8 = 2π x f0 x LAC8 = 10kΩ

ZC2 = 1/(2π x f0 x 1μF) = 1.6Ω

因此,ZNODE7 = 22kΩ || (10kΩ + 1.6Ω) || (10kΩ + 1.6Ω) = 4kΩ,ZNODE8 = 10kΩ || (10kΩ + 1.6Ω) || (10kΩ + 1.6Ω) = 3.3kΩ。

总线上的总阻抗ZBUS = ZNODE1 || ZNODE2 || ZNODE3 || ZNODE4 || ZNODE5 || ZNODE6 || ZNODE7 || ZNODE8 = 183Ω || (15kΩ / 5) || 4kΩ || 3.3kΩ = 157Ω,大于所需的最小总线端接电阻100Ω。图16显示了节点1(供电节点)处的总线波形。

图16 节点1(供电节点)处的总线波形

结语

本应用笔记阐述了为Home Bus系统选择合适“交流阻断”电感的标准。建议使用“耦合电感”或配置为“电感对”的两个独立电感。务必根据实际应用条件,采用本应用笔记中讨论的标准和方法,在试验台上确定所选的“交流阻断”电感是否合格。

本应用笔记还提供了示例和基准测量结果,以帮助读者为Home Bus应用选择合适的电感。

参考文献

MAX22088数据手册和MAX22088评估套件

MAX22288数据手册和MAX22288评估套件

Home Bus简介,Home Bus简介 | ADI公司

评论