一种低温漂输出可调带隙基准电压源的设计

2 CMOS带隙基准电压源电路结构

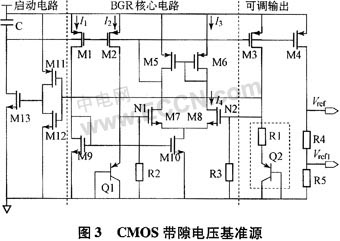

本设计是在SMIC 0.25μm CMOS工艺基础上完成的,设计中采用了一级温度补偿、电流反馈等技术。其电路结构如图3所示(不考虑虚线框R5部分)。

BGR核心电路中,晶体管Q1、Q2为使用标准CMOS工艺制造的二极管连接形式的PNP纵向三极管(BJT)。Q2和Q1的发射极面积的比为N,流过Q1和Q2的电流相等,这样△VBE就等于VTln(N)。流过电阻R1的电流I4是与热力学温度成正比的。流过M2、M3、M4的电流相等(I1=I2=I3),所以

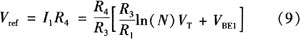

参考电压Vref为:

通过调节R3与R1的比值和Q2与Q1发射极面积的比值,可以使输出电压参考在室温下的温度系数为0。

本设计还具有输出可调的特点,设计中采用文献[2]提到的在运算放大器两输入端与地之间加电阻的方法。由式(9)可看出,在调节了k值

后,可以方便地调节R4的值来调节参考电压的输出大小,正是由于运算放大器两输入端的接地电阻R2、R3的增加,使得总的镜像电流通过电阻R4后可以方便地改变输出大小,相比文献[3]中的二次分压结构更简单,更节省面积。

该带隙基准源的电流源不仅用于提供基准输出所需的电流,也用于产生差分放大器所需的电流源偏置电压,大大简化了电路的版图。设计中采用了高增益NMOS差分对运算放大器,根据文献[4],实验仿真结果显示,对于电源电压的直流变化,低电源抑制比的运算放大器也能实现电压跟随,Vref输出稳定。而在电源电压有交流干扰、特别是信号频率较高(>30 MHz)时,Vref输出端也有同频的交流信号,幅度近似于电源干扰信号的幅度,这时Vref已不能认为是恒定的输出。原因是运算放大器输出信号与电源信号之间存在明显的相位差。解决的方法有两种:第1种是提高运算放大器的单位增益带宽;第2种是降低运算放大器本身的PSRR(电源抑制比)。第1种方法会增大电路消耗的功率,对于第2种方法,我们采用低PSRR(电源抑制比)的运算放大器就可以实现,相比于文献[5]中使用的PMOS差分对运算放大器,我们采用相对较低PSRR的NMOS差分对运算放大器。

本设计中还增加了带隙基准源的启动电路,因为带隙基准源存在两个电路平衡点,即零点和正常工作点,当电路处在零点时,整个电路中没有电流流过,电路不能正常工作。启动电路应满足两个方面的要求:一是确保总有电流流过参考源中的晶体管,使得零状态处的环路增益大于1,避免陷入零状态;二是参考源启动后,启动电路不应干扰参考源的正常工作。当基准源工作在零点时,节点N1、N2的电压等于0,基准源没有电流产生。启动电路的目的就是为了避免基准源工作在不必要的零点上。本文设计了图3中所示的启动电路,电路由M11、M12和M13构成。当电路工作在零点时,N2点电压为0,M13管导通,迅速提高节点N1、N2的电压,产生基准电流;这时节点N1的电压通过M11和M12组成的反相器,使M13管完全截止,节点N1、N2的电压回落在稳定的工作点上,基准源开始正常工作而启动电路中没有电流流过。

3 电路模拟和仿真结果

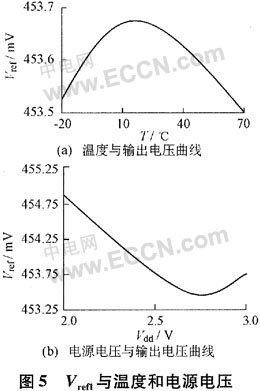

基于0.25μm BSIM3V3.2工艺模型,用cadence的spectre仿真工具对高精度输出可调带隙基准电压源电路进行了温度扫描和电源抑制比的模拟仿真。温度范围为-20℃~70 ℃,电源电压范围为2 V~3 V。在SMIC 0.25μm BSIM3V3.2工艺tt模型下的仿真所得结果为:输出Vref为1.012 V左右时,温度系数可达4.8×10-6/℃(如图4(a)所示),PSRR可达54 dB(如图4(b)所示);输出Vref1为453.7 mV左右时,温度系数可达4.4×10-6/℃(如图5(a)所示),PSRR为42 dB(如图5(b)所示)。

4 结束语

本设计是在传统带隙基准电压源理论的基础上,对电路进行改进而得到的高精度、输出可调的基准电压源,在设计中采用了一级温度补偿、电流反馈等技术,并在电路中增加了启动电路。仿真结果显示该设计温度系数高,可输出不同范围稳定的基准电压,达到预期的设计目标。

评论