AVR单片机(学习ing)—(九)、ATMEGA16的模数转换器—01

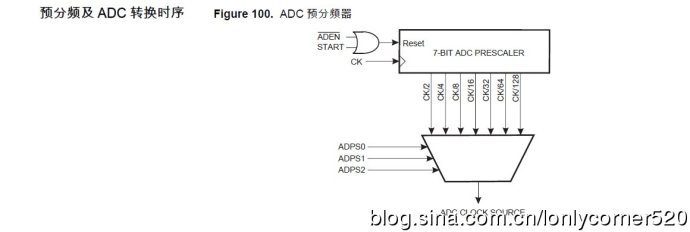

4、预分频及ADC 转换时序

在默认条件下,逐次逼近电路需要一个从50 kHz到200 kHz的输入时钟以获得最大精度。

如果所需的转换精度低于10 比特,那么输入时钟频率可以高于200 kHz,以达到更高的

采样率。

ADC 模块包括一个预分频器,它可以由任何超过100 kHz 的CPU 时钟来产生可接受的

ADC 时钟。预分频器通过ADCSRA 寄存器的ADPS 进行设置。置位ADCSRA 寄存器的

ADEN 将使能ADC,预分频器开始计数。只要ADEN 为1,预分频器就持续计数,直到

ADEN 清零。

ADCSRA寄存器的ADSC置位后,单端转换在下一个ADC时钟周期的上升沿开始启动。差

分转换时序见P197“ 差分增益信道” 。

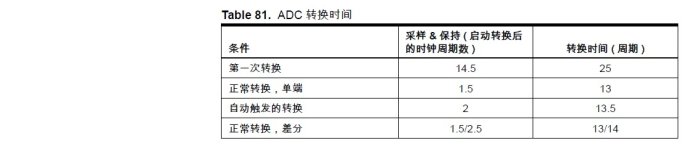

正常转换需要13 个ADC 时钟周期。为了初始化模拟电路,ADC 使能(ADCSRA 寄存器

的ADEN 置位) 后的第一次转换需要25 个ADC 时钟周期。

在普通的ADC 转换过程中,采样保持在转换启动之后的1.5 个ADC 时钟开始;而第一次

ADC转换的采样保持则发生在转换启动之后的13.5 个ADC时钟。转换结束后,ADC结果

被送入ADC 数据寄存器,且ADIF 标志置位。ADSC 同时清零( 单次转换模式)。之后软

件可以再次置位ADSC 标志,从而在ADC 的第一个上升沿启动一次新的转换。

使用自动触发时,触发事件发生将复位预分频器。这保证了触发事件和转换启动之间的延

时是固定的。在此模式下,采样保持在触发信号上升沿之后的2 个ADC 时钟发生。为了

实现同步逻辑需要额外的3 个CPU 时钟周期。如果使用差分模式,加上不是由ADC 转

换结束实现的自动触发,每次转换需要25 个ADC 时钟周期。因为每次转换结束后都要

关闭ADC 然后又启动它。

在连续转换模式下,当ADSC 为1 时,只要转换一结束,下一次转换马上开始。转换时

间请见 Table 81。

5、差分增益信道

当使用差分增益通道,需要考虑转换的确定特征。

差分转换与内部时钟CKADC2 同步等于ADC 时钟的一半。同步是当ADC 接口在CKADC2

边沿出现采样与保持时自动实现的。当CKADC2 为低时,通过用户启动转换( 即,所有的

单次转换与第一次连续转换) 将与单端转换使用的时间( 接着的预分频后的13 个 ADC 时

钟周期)。当 CKADC2 为高时,由于同步机制,将会使用14 个 ADC 时钟周期。在连续转

换模式时,一次转换结束后立即启动新的转换,而由于CKADC2 此时为高,所有的自动启

动( 即除第一次外) 将使用14 个 ADC 时钟周期。

在所有的增益设置中,当带宽为4 kHz 时增益级最优。更高的频率可能会造成非线性放

大。当输入信号包含高于增益级带宽的频率时,应在输入前加入低通滤波器。注意,ADC

时钟频率不受增益级带宽限制。比如,不管通道带宽是多少, ADC 时钟周期为6 μs,允

许通道采样率为12 kSPS。

如果使用差分增益通道且通过自动触发启动转换,在转换时ADC 必须关闭。当使用自动

触发时, ADC 预分频器在转换启动前复位。由于在转换前的增益级依靠稳定的ADC 时

钟,该转换无效。在每次转换( 在寄存器 ADCSRA 的ADEN 位中 写 “0” 接着为“1”),通

过禁用然后重使能ADC,只执行扩展转换。扩展转换结果有效。

6、改变通道和基准源

ADMUX寄存器中的MUXn及REFS1:0通过临时寄存器实现了单缓冲。CPU可对此临时寄

存器进行随机访问。这保证了在转换过程中通道和基准源的切换发生于安全的时刻。在转

换启动之前通道及基准源的选择可随时进行。一旦转换开始就不允许再选择通道和基准

源了,从而保证ADC 有充足的采样时间。在转换完成(ADCSRA 寄存器的ADIF 置位) 之

前的最后一个时钟周期,通道和基准源的选择又可以重新开始。转换的开始时刻为ADSC

置位后的下一个时钟的上升沿。因此,建议用户在置位ADSC 之后的一个ADC 时钟周期

里,不要操作ADMUX 以选择新的通道及基准源。

使用自动触发时,触发事件发生的时间是不确定的。为了控制新设置对转换的影响,在更

新ADMUX 寄存器时一定要特别小心。

若ADATE及ADEN都置位,则中断事件可以在任意时刻发生。如果在此期间改变ADMUX

寄存器的内容,那么用户就无法判别下一次转换是基于旧的设置还是最新的设置。在以下

时刻可以安全地对ADMUX 进行更新:

1. ADATE 或ADEN 为 0

2. 在转换过程中,但是在触发事件发生后至少一个ADC 时钟周期

3. 转换结束之后,但是在作为触发源的中断标志清零之前

如果在上面提到的任一种情况下更新ADMUX,那么新设置将在下一次ADC 时生效。

当改变差分通道时要特别注意。一旦选定差分通道,增益级要用125 μs 来稳定该值。因

此在选定新通道后的125 μs 内不应启动转换。或舍弃该时间段内的转换结果。

7、ADC 输入通道

选择模拟通道时请注意以下指导方针:

工作于单次转换模式时,总是在启动转换之前选定通道。在ADSC 置位后的一个ADC 时

钟周期就可以选择新的模拟输入通道了。但是最简单的办法是等待转换结束后再改变通

道。

在连续转换模式下,总是在第一次转换开始之前选定通道。在ADSC 置位后的一个ADC

时钟周期就可以选择新的模拟输入通道了。但是最简单的办法是等待转换结束后再改变

通道。然而,此时新一次转换已经自动开始了,下一次的转换结果反映的是以前选定的模

拟输入通道。以后的转换才是针对新通道的。

当切换到差分增益通道,由于自动偏移抵消电路需要沉积时间,第一次转换结果准确率很

低。用户最好舍弃第一次转换结果。

8、ADC 基准电压源

ADC的参考电压源(VREF)反映了ADC的转换范围。若单端通道电平超过了VREF,其结果将

接近0x3FF。VREF 可以是AVCC、内部2.56V 基准或外接于AREF 引脚的电压。

AVCC通过一个无源开关与ADC相连。片内的2.56V参考电压由能隙基准源(VBG)通过内部

放大器产生。无论是哪种情况,AREF 都直接与ADC 相连,通过在AREF 与地之间外加

电容可以提高参考电压的抗噪性。VREF 可通过高输入内阻的伏特表在AREF 引脚测得。

由于VREF 的阻抗很高,因此只能连接容性负载。

如果将一个固定电源接到AREF 引脚,那么用户就不能选择其他的基准源了,因为这会导

致片内基准源与外部参考源的短路。如果AREF 引脚没有联接任何外部参考源,用户可以

选择AVCC 或1.1V 作为基准源。参考源改变后的第一次ADC 转换结果可能不准确,建

议用户不要使用这一次的转换结果。

9、相关寄存器

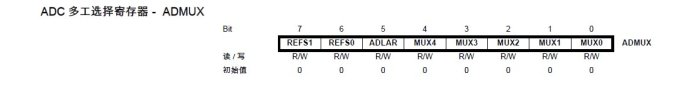

1)ADMUX

• Bit 7:6 – REFS1:0: 参考电压选择

如Table 83 所示,通过这几位可以选择参考电压。如果在转换过程中改变了它们的设置,

只有等到当前转换结束(ADCSRA 寄存器的ADIF 置位) 之后改变才会起作用。如果在

AREF 引脚上施加了外部参考电压,内部参考电压就不能被选用了。

• Bit 5 – ADLAR: ADC 转换结果 左对齐

ADLAR影响ADC转换结果在ADC数据寄存器中的存放形式。ADLAR置位时转换结果为左

对齐,否则为右对齐。ADLAR 的改变将立即影响ADC 数据寄存器的内容,不论是否有

转换正在进行。

• Bits 4:0 – MUX4:0: 模拟通道与增益选择位

通过这几位的设置,可以对连接到ADC 的模拟输入进行选择。也可对差分通道增益进行

选择。细节见Table 84。如果在转换过程中改变这几位的值,那么只有到转换结束

(ADCSRA 寄存器的ADIF 置位) 后新的设置才有效。

评论