TQ2440国嵌学院gboot-时钟初始化

通过选择HDIVN

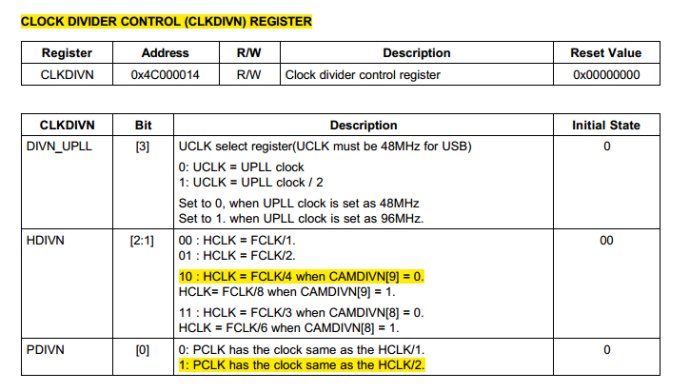

因此设定HDIVN=2,也就是01;设定PDIVN=1,也就是0。DIVN_UPLL不设定,组合起来也就是在CKDIVN寄存器里写入0X5(0b000101),寄存器的地址是0x4c000014。

如何设定CPU到异步模式呢?

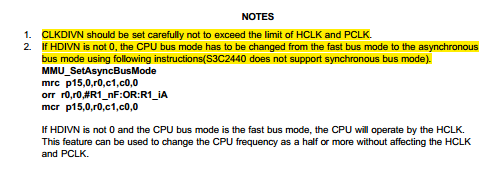

为什么要设定CPU到异步模式呢?看下面介绍:

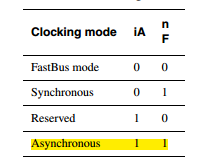

翻译可知,当HDIVN不等于0的时候,要设定CPU到异步模式,HDIVN不等于0代表什么呢?首先看等于0,等于0代表FCLK=HCLK,也就是CPU核工作时钟等于总线时钟,当2者相同的时候是同步,不相等就是异步模式。因此要设定到异步模式。如何设置到异步模式?

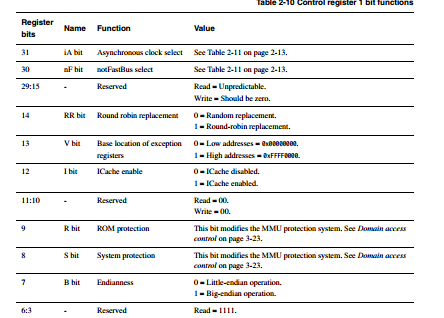

代码上面也有给出,通过设定CP15的C1寄存器的nF和iA位都为1即可。

最后来看设定FCLK的频率:

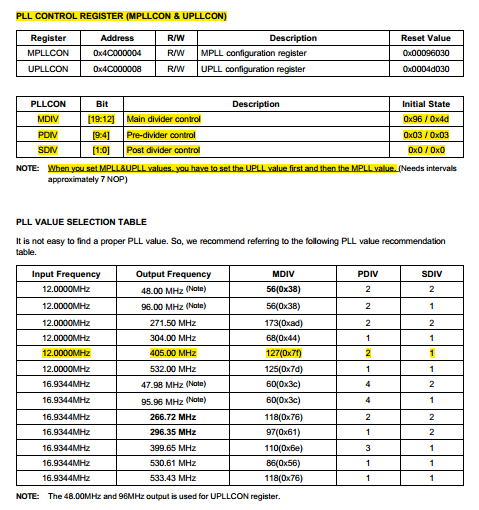

首先我们采用的CPU的工作频率是405MHZ,也就是MDIV=0X7F,PDIV=10;SDIV=1

全部代码:

#define CLKDIVN 0x4c000014

#define MPLLCON 0x4c000004

#define MPLL_405MHZ ((127<<12)|(2<<4)|(1<<0))

init_clock:

评论