天然气体积修正仪数据采集模块设计

为了实现快速状态转换同时增强稳定性,避免出现毛刺现象,A/D转换器的时序控制采用多进程有限状态机来实现。

(1) 时序逻辑

时序逻辑进程STATE_TRANS负责状态转换,当时钟信号SYS_CLK上升沿到来时,判断转换条件使状态机转入相应状态。

(2) 组合逻辑

组合逻辑进程STATE_BEHV负责状态输出,当状态变量ST发生变化时,产生对应此状态的CNV_ST,AD_RD AD_CS,CH(0为第一通道,1为第二通道)及STATUS相应输出。

(3) 计数逻辑

定义P0进程,敏感参数为CNV_ST,当一组数据采样结束(CNV_ST信号由0变为1),如果已经采集10组数据,则置位FULL信号,表示采样过程已经结束。

2.2.3 滤波器设计

A/D转换后的数据还不能立即送入处理器中处理,为了提高数据的准确性,设计滤波单元对数据进行处理。滤波滤波器设计实现经A/D转换后的数据滤波处理及数据的输出。

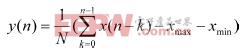

数字滤波模块的滤波算法采用中位值平均滤波法,相当于“中位值滤波法”+“算术平无度滤波法”,该方法计算简单、速度快,还可消除由于脉冲干扰所引起的采样值偏差,使得经滤波后的输出信号为“干净”信号,可直接用于工业控制。中位值平均滤波法的时域差分方程是:本文引用地址:https://www.eepw.com.cn/article/188538.htm

本系统设计10组数据进行滤波处理,取N=8。为了节约FPGA内部资源,滤波器的设计中采用移位寄存器代替除法器来实现平均滤波部分的算法。滤波模块的设计从采样数据的输入、数值累加、去极值、求平均值到数字量的输出共5个处理步骤,并且整个数据处理是“单流向”的,前一步骤的输出是下一步骤的输入,符合流水线设计要求。采用流水线设计方法可以提高系统的工作频率,从宏观上看数字滤波模块不占用额外的处理时间,对于超高速A/D转换控制中显得格外重要。从VHDL语言的角度看,流水线操作是用面积换速度思想的具体体现[3]。

定义滤波器端口类型见表2所示。

从仿真图中可以看出,当时钟处于上升沿,AD_START变为高电平时,启动A/D转换,依次读2个通道的数据。当读满10组时,进行滤波处理。当CPU发出读信号时,数据读出。可见,设计的A/D控制器和滤波器完全符合设计要求。

对设计程序进行编译,可以看出,EP1C12Q240C8总的逻辑元数目为12 060,本控制模块只占用了227个,完全达到数据采集及滤波处理功能,极大地减轻了CPU的负担,可以让CPU专注于其他的任务。是一种可行且值得推广的方法。

3总体功能仿真及编译结果

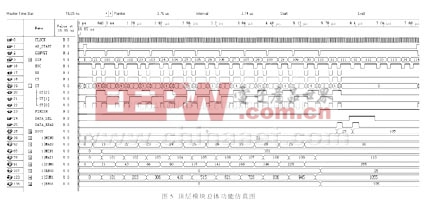

设计完成,生成顶层模块。该模块可直接加入到体积修正仪的SOPC设计中。其总体功能仿真如图5所示。

从仿真图中可以看出,当时钟处于上升沿,AD_START变为高电平时,启动A/D转换,依次读2个通道的数据。当读满10组时,进行滤波处理。当CPU发出读信号时,数据读出。可见,设计的A/D控制器和滤波器完全符合设计要求。

对设计程序进行编译,可以看出,EP1C12Q240C8总的逻辑元数目为12 060,本控制模块只占用了227个,完全达到数据采集及滤波处理功能,极大地减轻了CPU的负担,可以让CPU专注于其他的任务。是一种可行且值得推广的方法。

评论