基于AD9268的短波接收全数字传输结构

2 高速大量化位数的ADC

AD公司(Analog Device)推出的AD9268就是一款可以满足系统需求的高速高量化位数的ADC。

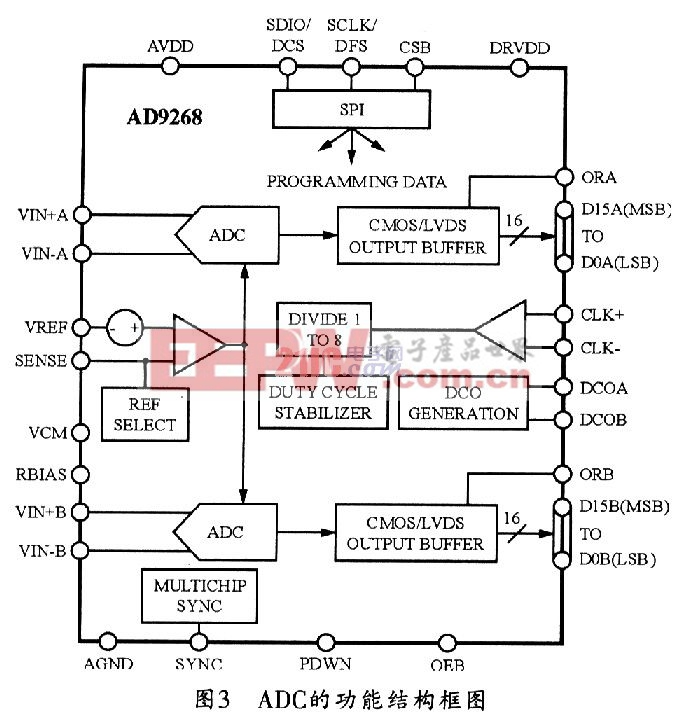

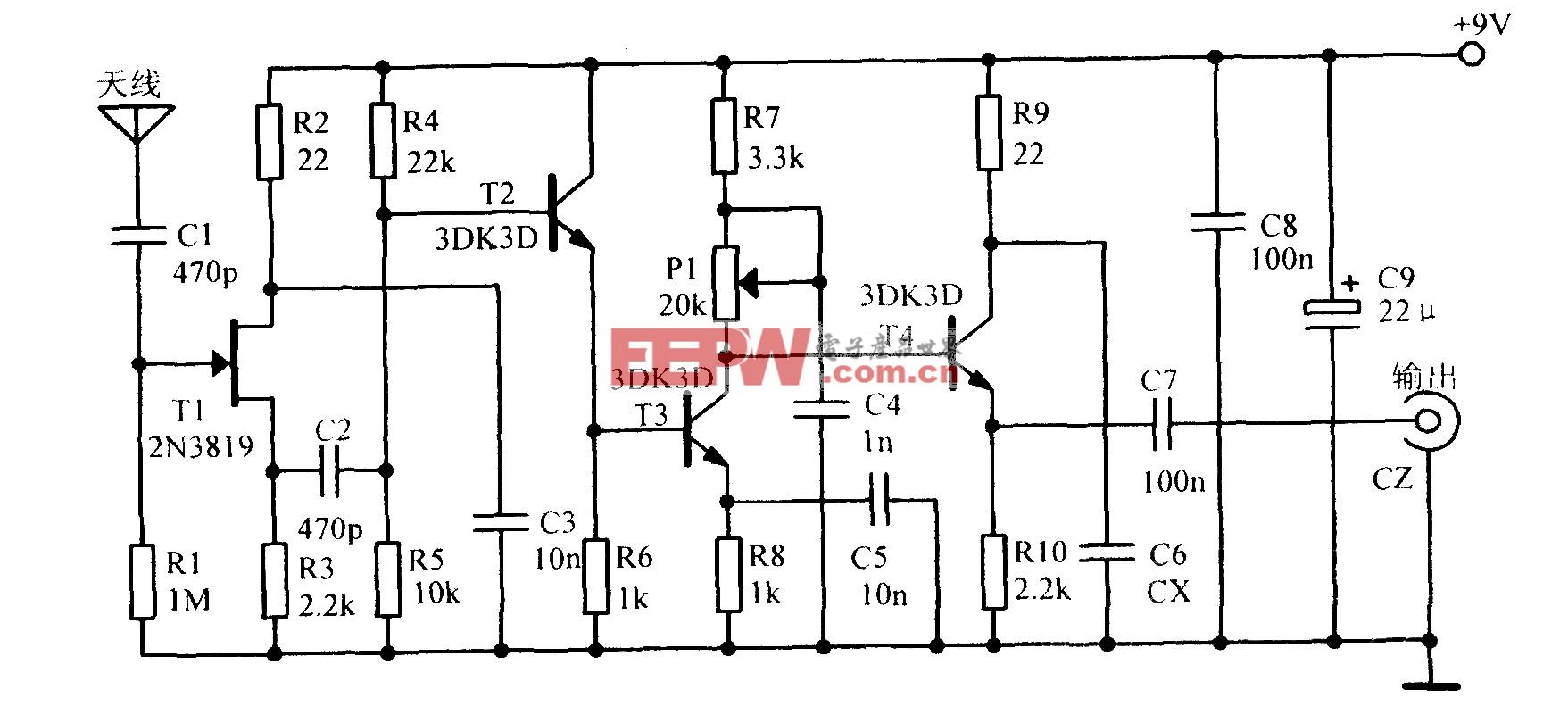

图3所示是AD9268芯片的功能结构框图。该器件对于双路双通道输入信号可以并行进行高速的采样量化,显然,当输入为正交I、Q信号时,它可以在采样率不变的条件下,获得更高的信号无失真带宽。

该器件的数字信号量化数据位为16 bit,同源时钟和信号以差分线的形式输出,从而保证了输出信号优良的信号完整性。

芯片通过SPI接口进行工作模式参数寄存器的配置。值得一提的是,该芯片还提供有多片之间的同步接口,这就为系统进行多通道的信号测向处理做好了伏笔。

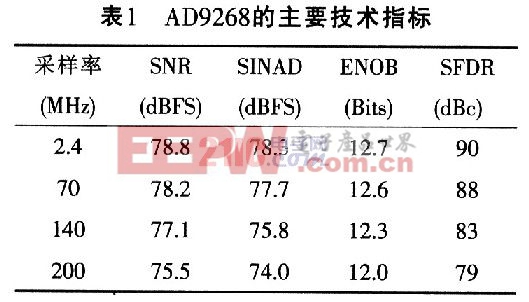

AD9268的主要技术指标如表1所列。通过表1可见,该芯片的主要指标十分出色,能够满足复杂信号条件下的信号接收。使用该芯片足以实现系统对短波频段的采样完全覆盖。

AD9268芯片的管脚兼容CMOS/LVDS/LVPECL等电平。模拟、数字均使用1.8 V供电。芯片典型功耗为750 mW,实验室测试最大功耗为875 mW。

3 时钟产生单元

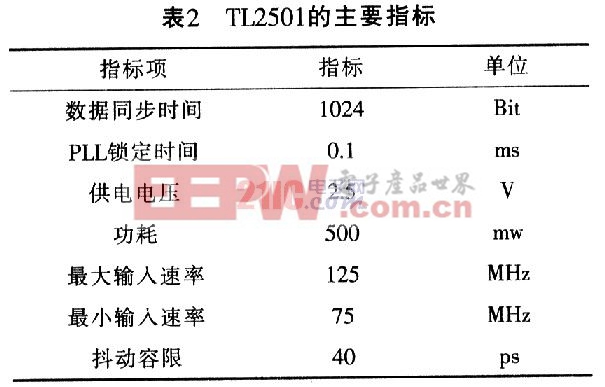

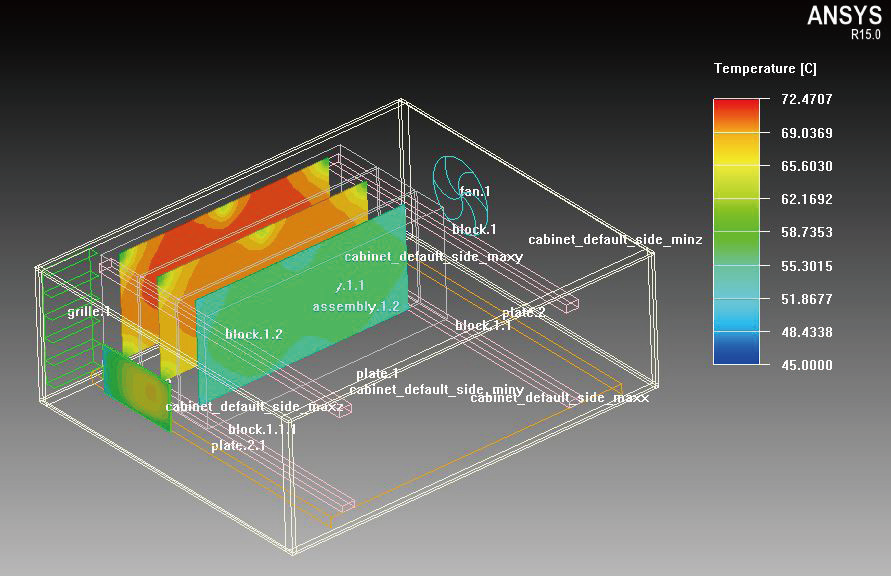

对于光纤通信系统来说,数据时钟的准确性和稳定性是十分重要的,试验证明,它会直接影响信号传输的误码率。ICS8442是由ICS (Inte-grated Circuit Systems,Ine)推出的一款具有很好频综性能的集成芯片。

ICS8442芯片的主要功能是将普通晶振的时钟信号转换为高稳定的差分电平时钟信号。输出频率范围从31.25 MHz~700 MHz。

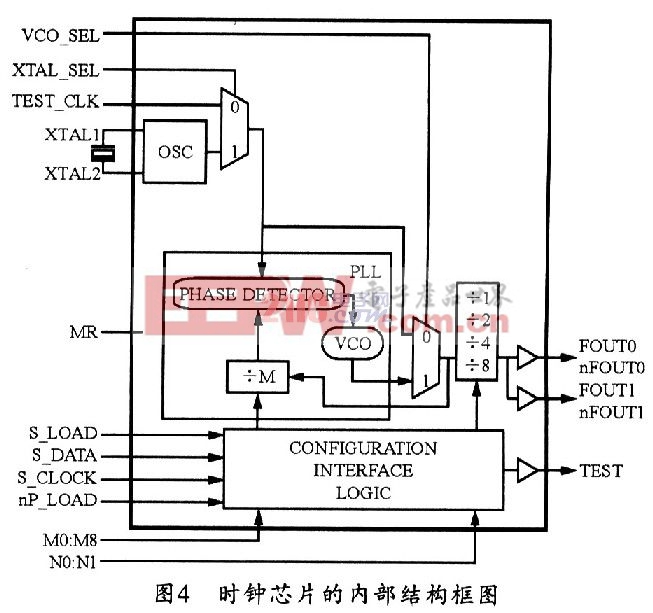

图4所示是ICS8442的内部结构框图。该芯片可对输入时钟进行相位锁定和频率综合,并可通过控制接口实现不同输出电平制式的切换。

输出频率可通过控制寄存器M、N进行设置,ICS8442使用3.3 V电源,最大功耗为500 mW。

评论