采用IDDR的亚稳态问题解决方案

只需少量代码

在《Virtex-4用户指南》的328~329页,举例说明采用VHDL和Verilog语言编写的IDDR原语的例化。以下采用Verilog语言的IDDR原码例化的典型实例:

defparam IDDR_INT2.DDR_CLK_EDGE = SAME_EDGE_PIPELINED;

defparam IDDR_INT2.INIT_Q1 = 1'b1;

defparam IDDR_INT2.INIT_Q2 = 1'b1;

defparam IDDR_INT2.SRTYPE = SYNC;

IDDR IDDR_INT2( .Q1(sync_data),

.Q2(signal_noload), .C(CLK_2X),

.CE(1'b1), .D(async_data),.R(), .S());

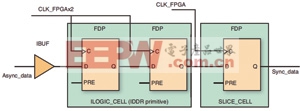

在图3中看到全新的布局图。 用这种方法将寄存器链放置在两个单元:前两个寄存器放置在ILOGIC单元中,另一个寄存器则放置在SLICE单元中(这里选择的链具有3个寄存器和2个不同的时钟,其中一个时钟速度是另一个的两倍)。

图3 显示IDDR替代的同步器链

整体而言,亚稳态问题会给设计带来不便,但采用一些快速便捷的解决方案(如以一种新的方式使用IDDR原语)就能大幅降低设计发生亚稳态问题的几率。大家应在创建设计时就采用上述方法,而不应事后亡羊补牢,这样就能创建出既能灵活应对亚稳性问题,而且所占面积、性能和成本又得到优化的架构。

评论