一种针对多级串联模拟电路的可测性设计技术

3 与边界扫描技术的兼容性

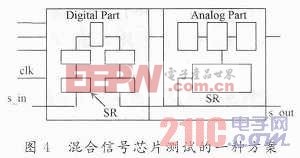

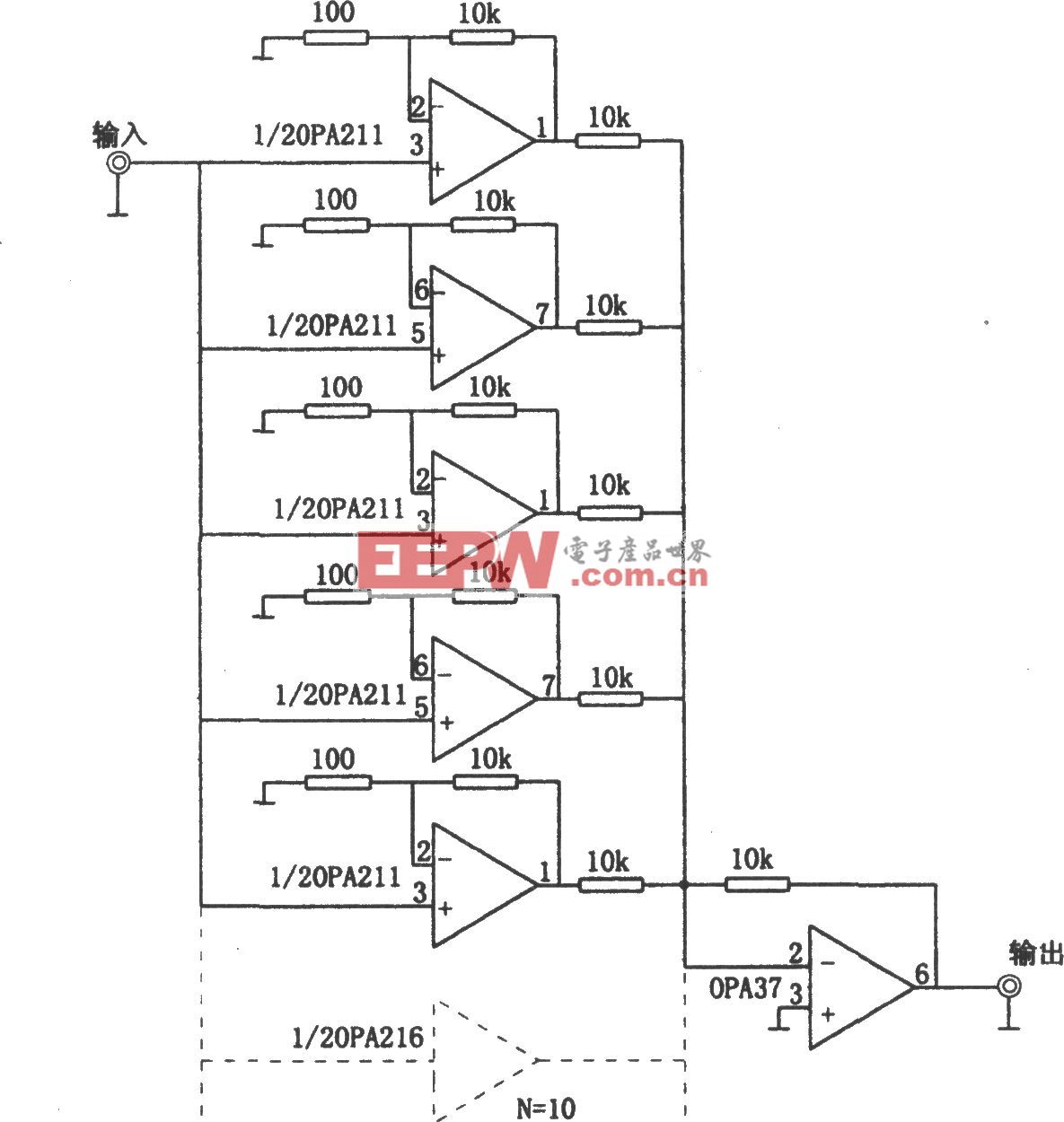

边界扫描测试技术在降低产品测试成本,提高产品质量和可靠性以及缩短产品上市时间等方面有显著的优点,目前在数字电路的测试中已得到很多应用。它也可应用于混合信号测试,图4就是一种混合信号芯片测试方案。本文设计的DFT结构中指令寄存器串接在IEEE 1149.1标准中的扫描寄存器后,共用时钟信号,可以进行联合测试,并且进一步减少了模拟部分额外引出的端口数。

4 结语

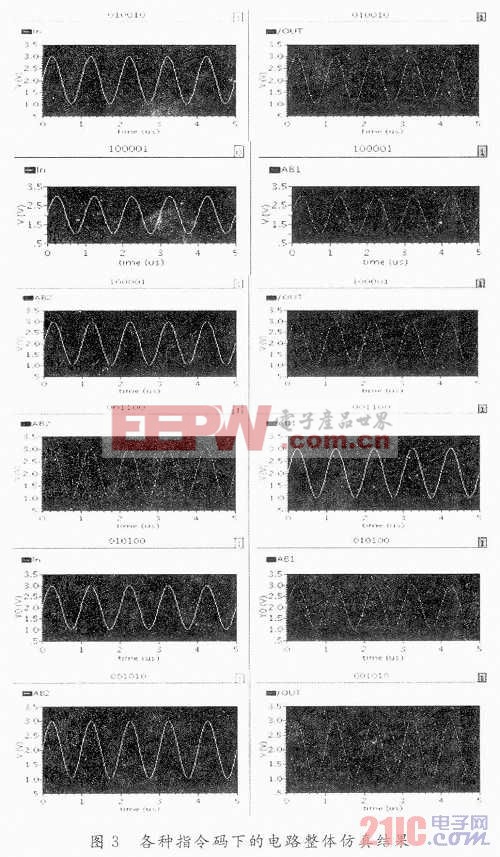

本文针对串联结构的模拟集成电路提出一种可测性设计结构,提高了电路的可控制性及可观察性,实现对电路整体以及内部单一或几个相邻模块的测试。仿真分析证明,该结构简单有效,只需额外引出5个PAD,数目少,灵活性高,不随模块数增加而变化,并可兼容边界扫描技术。不过,在提高可测试性的同时,会在一定程度上增加芯片的面积和功耗。

电路相关文章:电路分析基础

pic相关文章:pic是什么

评论