基于GC5016的并行多通道接收机研究

2 模块功能描述

2.1 数字下变频(DDC)

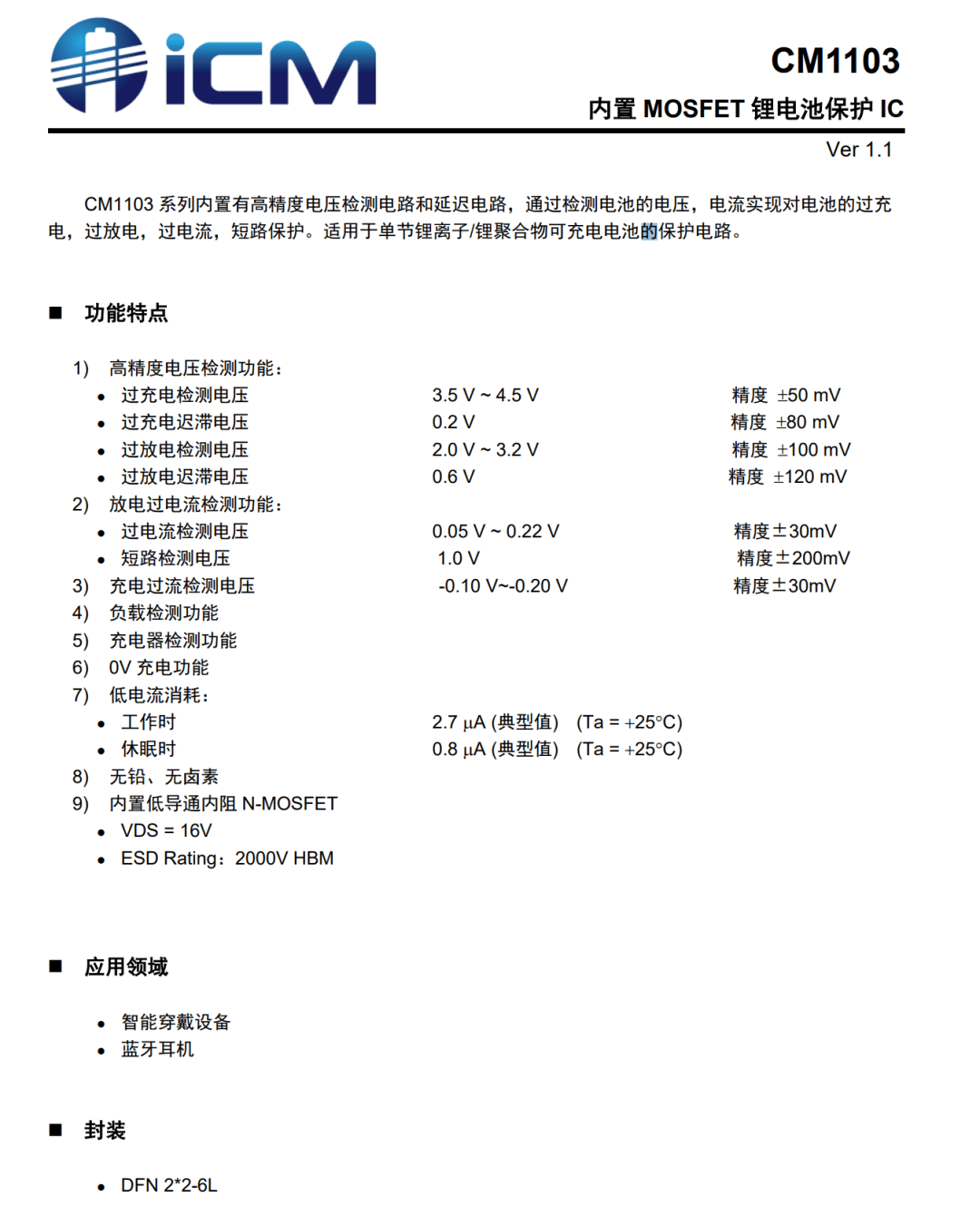

GC5016是一种灵活的宽带四信道数字上下变频器,可设计用于高速、高带宽的数字信号处理应用,例如3G蜂窝收发基站的发送和接收信道,也可用于通用目的的数字滤波。四个相同的处理信道可以独立地配置为上变频,下变频或者两上两下的组合。本文将它们配置为四个下变频通道,作为通用的数字滤波器使用。在四信道模式下输入速率高达160 MSPS,无杂散动态范围为115 dB,16个255阶的FIR滤波器,64个并行输入/输出位,提供灵活的I/O选项。

在下变频模式中,信道接收实数据或者复数据,在选定的载波频率上解调,并进行抽取,自动增益放大,产生20位的输出。信道的输出信号经过格式化后,以实数或者复数的形式加到四个输出端口,完成数字下变频。

下变频信道处理流程中,首先经过接收输入格式器(Receive Input Formatter,RINF)将ADC采样的数据格式转化为复输入格式。在混频段,通过接收输入信道选择(Receiver Input Selection,RSEL)、数控振荡器(Numericallv Controlled Oscillator,NCO)和复混频逻辑,将中频信号载波频率混频搬移至0 Hz,形成零中频信号或称基带信号。混频之后是5级的积分梳状(Cascade Integrator Comb)抽取滤波器,提供1~256的整数倍抽取和复滤波。可编程的有限冲击响应滤波器(Programmable Finite Impulse Response Filter,PFIR)提供CIC的矫正,频谱锐化以及进一步的抽取,PFIR的抽取率是1~16倍。复功率计对信号增益进行监视,输出下变频之后的信号。

2.2 基带处理

软件无线电的基带处理需要具有如下特征:强大的运算能力、完全的灵活性、模块化、可增减性和开放的体系结构。FPGA以很高的集成度和灵活的可重新配置功能,非常适合软件尢线电基带处理领域。在FPGA中可以完成信号的载波估计和同步,符号时钟估计和同步,信道均衡,信号的解调、解扩等等。通过上位机的控制和交互,完成部分乃至全部的基带处理,并将数据通过PCI总线送入计算机,依靠廉价的PC以及其组成的计算机网络完成部分基带和上层数据的处理工作。

2.3 重配置电路

软件无线电要求在一个通用的硬件平台上实现各种通信功能,因此可重构性必然成为软件无线电的根本特性。FPGA可以根据不同的配置信息构建不同的硬件电路,再配合微处理器或者其他可编程器件来模拟FPGA的配置时序,这就可以实现对FPGA重配置的控制。在此思想指导下,本文利用CPLD的通用I/O口产生配置时序,通过PCI总线传送新的配置文件,在上位机的控制下,实现了对FPGA的重新配置。上/下变频芯片GC5016的重配置与FPGA相同,被控芯片和上位机的相互配合即在一定程度上实现了系统的在线重构技术。PCI9054芯片用于FPGA,CPLD和PCI总线之间的桥接工作,已经相当成熟,在此不再赘述。

3 滤波器理论分析

GC5016芯片包含两类滤波器,CIC(级联积分梳状)滤波器和PFIR(可编程有限冲击响应)滤波器。CIC滤波器已被证明在高速抽取或插值系统中是非常有效的单元。在下变频中CIC可以将中频采样的信号按需要降低到基带。CIC滤波器是IIR和FIR滤波器的组合,它能用简单的结构、较少的资源灵活地实现输入、输出数字信号的速率变换,往往在DDC中用作第一级处理。

FIR滤波器,即有限冲击响应滤波器是指冲激响应函数h(n)为有限个值的数字滤波器。FIR滤波器具有许多独特的优越性,除了可以做成具有严格的线性相位外,还可以满足任意的幅度特性要求,也不存在不稳定问题,且设计相对成熟。

理论分析中采用了实信号形式进行分析,而实际的芯片处理通过模块复制实现了复信号的处理。

3.1 CIC滤波器

CIC滤波器用来实现第一级的整数倍抽取,如图3所示。该滤波器的冲激响应具有如下形式:本文引用地址:https://www.eepw.com.cn/article/186573.htm

评论