基于可编程计数器的时序逻辑电路设计

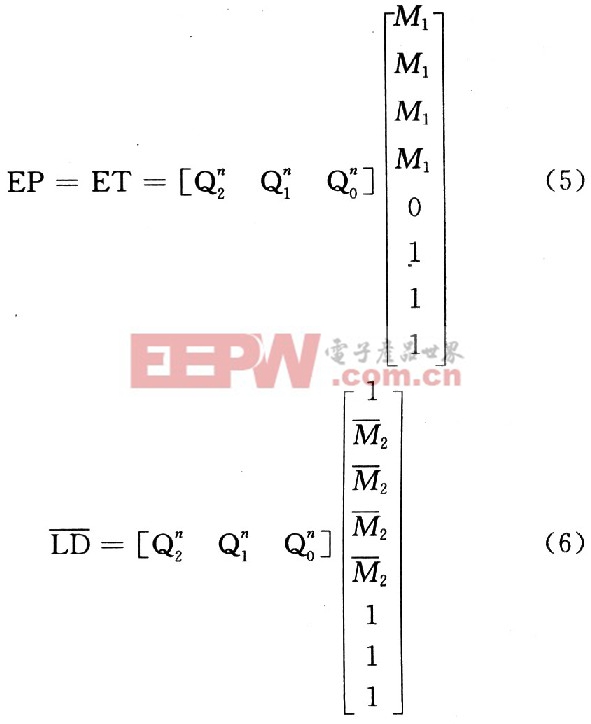

其中,不使用的101,110和111状态,将EP,ET及

作出74LSl61计数器预置输入变量的卡诺图及画包围圈化简如图5所示,各预置输入变量的最简逻辑表达式为:

由图4所示的状态图,写出输出函数Z的矩阵方程式:

其中,不使用的101,110和111状态的输出设置为O,亦可设置为1。

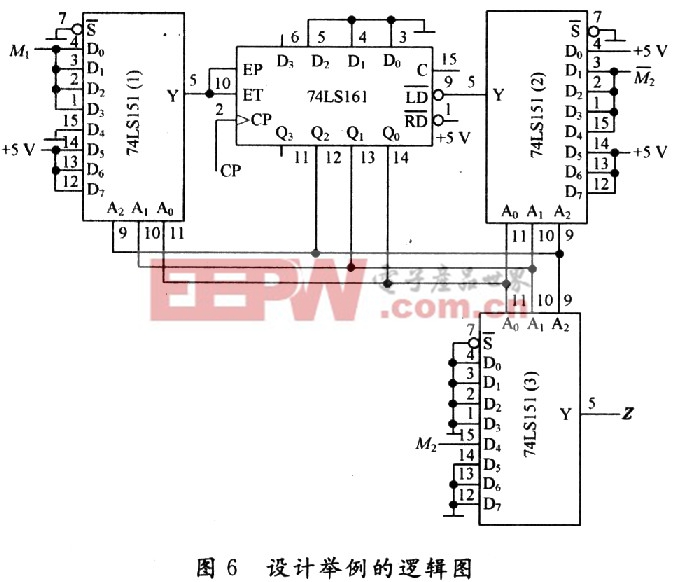

用1个74LSl61可编程计数器,3个8选数据选择器74LSl51按式(5)~(8)画出逻辑图如图6所示。

3 结语

基于可编程计数器的时序逻辑电路设计技术,提出了设计一般时序逻辑电路的状态分配原则及设计步骤,具有实际应用意义。

需要指出,当用单片74LSl61可编程计数器控制EP,ET及![]() 构成模数N16的任意进制计数器时,无输入变量,所用状态仅最后一个是非二进制时序,其余均为二进制时序。由功能表可知,需将EP,ET设置为常数1且不需选择,可将图2所示的一般结构中控制EP,ET的数据选择器简化掉,而

构成模数N16的任意进制计数器时,无输入变量,所用状态仅最后一个是非二进制时序,其余均为二进制时序。由功能表可知,需将EP,ET设置为常数1且不需选择,可将图2所示的一般结构中控制EP,ET的数据选择器简化掉,而![]() 控制函数仅在最后状态为O,可用门简单控制。

控制函数仅在最后状态为O,可用门简单控制。

评论