基于快速传输海量存储的电能质量监测系统

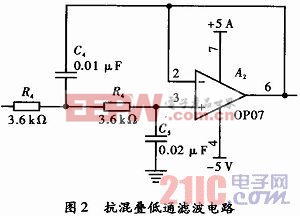

2.2.2 抗混叠滤波电路设计

抗混叠滤波电路实质是迫使信号通过一个有限带宽的低通滤波器,使输入到A/D转换器的信号为有限带宽信号,并且以很小的衰减让有效的频率信号通过,而抑制这个频带以外的频率信号,从而防止信号的频谱发生混叠及高频干扰。该滤波器的截止频率为采样频率的一半。谐波测量系统在信号每个周期采样128点即采样频率为128×50=6 400 Hz,所以抗混叠滤波器的截止频率为采样频率的一半即3200Hz。本文引用地址:https://www.eepw.com.cn/article/178674.htm

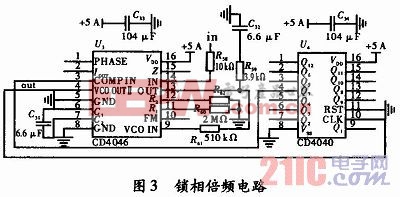

2.2.3 锁相倍频电路的设计

虽然我国电网的频率规定为50 Hz,但实际电网的频率受供电负荷不平衡影响会有一些波动。如果以定步长对电力系统的信号进行采样,会使实际每个工频周期内采样点的起始时刻、采样点个数出现差异,这种差异将导致栅栏效应和频谱泄露,使信号频谱分析的结果产生误差。为尽量减小这种误差,设计锁相倍频电路跟踪系统频率的波动。

锁相倍频电路由相位比较器、环路滤波器、压控振荡器和分频器4部分构成,具体电路如图3所示,电路工作原理为:输入电压信号通过14脚接入CD4046的相位比较器,经锁相环的相位锁定后,由CD4040的4脚输入CD4046的3脚的信号频率与原输入信号的频率一致。此时由CD40 46产生一个频率为128倍于输人信号的脉冲作为A/D的采样频率。在此,将锁相倍频电路输出端口与ADS8364的/HOLDX相连,以满足同步采样的需要。

评论