PCB板时钟电路的电磁兼容设计

3.3 端接设计

时钟驱动芯片不用的输出管脚,比如:空载(开路),由于管脚开路全反射可能会引起时钟高次谐波的电磁干扰问题。在单板上加备用端接是解决这个问题的一种方案,但是备用端接采用电阻还是电容或者其他的端接方式时主要看空载所引起的电磁干扰的频点。如果采用电阻端接,就要考虑由此带来的功耗和驱动器的驱动电流;如果采用电容端接,可能会增加某些其他频点的电磁干扰,因此电容的大小时要优化电容值;如果不用管脚没有端接,但是已经通过试验证明了电磁干扰有足够的裕度,就没必要对未用管脚进行额外的备用端接处理。

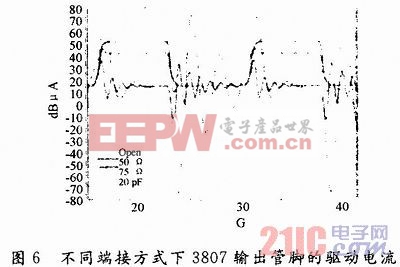

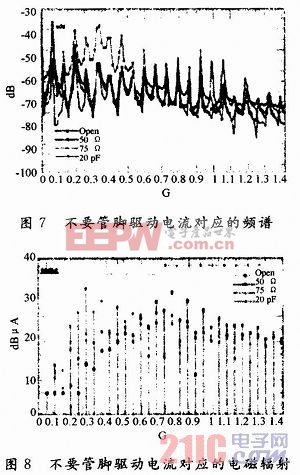

下面以3807数字时钟芯片为例,用仿真试验的结果来解释备用端接的作用。图6~图8表示了芯片不用的输出管脚时在开路、接50 Ω对地电阻、接75 Ω对地电阻、接20 pF对地电容等方式时,驱动脚的电流、频谱分布及驱动电流所产生的电磁辐射。本文引用地址:https://www.eepw.com.cn/article/177763.htm

从上面的结果可以看出:

(1)开路时的驱动电流最小,但有明显的窄脉宽振铃。就说明如果驱动器不用管脚空载(开路),驱动器的功耗最小。但是由此会带来一个不利的方面,那就是驱动电流的频谱中高频分量会变大,有可能导致高频的电磁干扰问题。这一点通过图7和图8中的开路驱动电流的频谱和电磁干扰曲线(蓝色曲线)也可以得到验证。

(2)如果驱动器不用管脚用电阻端接,驱动电流会变大,但是驱动电流中的振铃现象明显减弱。采用小电阻端接,可以改善驱动电流的振铃,但是会增加驱动电流,功耗变大;如果采用大电阻端接,可以减小驱动电流,但是会使得驱动电流出现振铃现象(开路是电阻端接的一个极限)。通过仿真结果看,选择75欧姆端接电阻一方面可以使得驱动电流不会很大,另一方面驱动电流的振铃也不是很明显。

(3)如果驱动器不用管脚采用电容端接,驱动电流的峰值变大,同时驱动电流脉冲的宽度也变大。这就表示驱动电流中的低频分量会明显变大,这就要注意低频段谐波的电磁干扰问题。图7和图8中对应电容端接的驱动电流的频谱曲线和电磁干扰曲线的低频分量明显变大也验证了这个问题。

4 结语

本文主要就对如何降低时钟(干扰源)的干扰进行了分析和总结,因此可以得出以下如何切断时钟干扰的传播途径的结论。一是将时钟电路的基波和谐波能量最大程度的约束到指定的范围之内(这些能量传输需要的电路包围的面积越小越好);其二是有效建立时钟电路区域与输入输出接口线路的隔离。由此可以在时钟电路设计时可以通过布局和布线来达到优化电磁兼容设计的目的。

DIY机械键盘相关社区:机械键盘DIY

评论