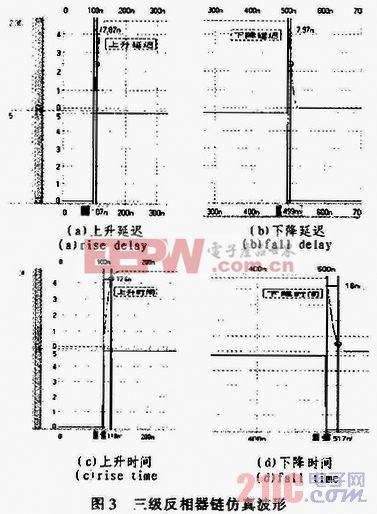

由图3(a)(b)(c)(d)可知,在输出缓冲器设计为三级反相器链的情况下,缓冲器的上升时间tr=17.6 ns,tf=16 ns,td=15.84 ns。

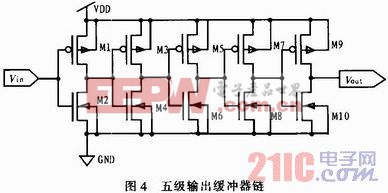

2)把输出缓冲器设计为五级反相器链,如图4所示。

图4中各个PMOS管和NMOS管的尺寸分别为(取S=2.72)。

则同样通过HSPICE仿真软件,在0.6μm CSMC 2P2MCMOS工艺库下的仿真结果为(负载为100 pF电容,1 kΩ电阻)。如图5(a)(b)(c)(d)所示,主要考虑仿真结果中的输出反向器链的上升时间tr、下降时间tf、上升延迟和下降延迟td。

电能表相关文章:电能表原理

评论