触摸屏控制器芯片中的高精度低功耗ADC设计

DAC级间耦合电容值的优化设计

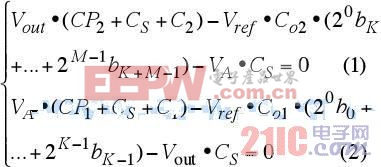

图1中CP1、CP2分别为A、B两点到地的寄生电容。转换过程中A、B电荷守恒,于是可得:

C1、C2分别为低权位和高权位子DAC的总容值;CO1和CO2分别是低权位和高权位子DAC的单位容值;K=8,M=4。解方程组,得到输出电压为:

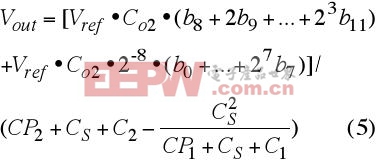

由电路参数可知:C02=4C,C01=2-2C=2-4C02,所以:

以高权位DAC为基准,输出应有如下表达式:本文引用地址:https://www.eepw.com.cn/article/162538.htm

比较式(4)和式(5),可得:

比较式(4)和式(5),可得:

分析耦合电容公式(6)可知,耦合电容大小与低权位寄生电容有关,而与高权位寄生电容无关。高权位DAC的寄生电容不影响高低权位间的比例关系,只影响最终输出电压的绝对值。从输出表达式(5)中可以看到,高权位寄生电容出现在分母中,它会使输出绝对值变小,所以应该尽量减小高权位寄生电容值。低权位寄生电容也会使输出绝对值变小,但这个影响很小,和高权位寄生电容的影响相比,几乎可以忽略不计。根据(6)式,低权位寄生电容出现在耦合电容表达式的分子上, 所以低权位寄生电容越大,耦合电容值也越大,通过增大耦合电容值就可以消除低权位寄生电容的影响。

寄生电容通常由电容极板和屏蔽层或阱形成,因此寄生容值和高低权位寄生电容大小有关系。所以,为了减小高权位寄生电容对输出电压的影响,在版图设计时,应尽量减小寄生。

综合考虑输入电容要求及电容匹配精度后,选取做在N阱里的双poly电容。单位电容取为400fF ,权位电容采用单位电容并联结构,以提高匹配性。采取中心对称布局,电容上覆盖metal2作静电屏蔽层;N阱和metal2均接地。寄生电容主要包括电容上极板和metal2之间、走线与metal2之间的寄生电容等。虽然高4位子DAC的寄生电容不影响权位间比例关系,但它会使输出电压值降低,以致需要更高精度的比较器。所以将覆盖在高4位子DAC电容上的metal2开孔,减小其寄生容值。

比较器的设计

由于DAC模块采用的是开关电容网络,在此将设计一个可消除直流失调电压的开关电容比较器。开关电容比较器使用组合开关电容和开环比较器。它的优点是,差分信号可用单端电路进行比较,且可对开环比较器直流失调电压自动校零。

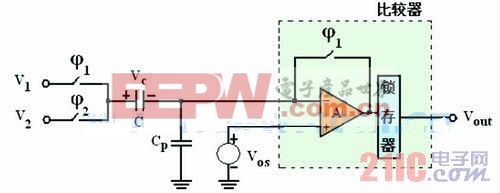

本文采用如图2所示结构设计SAR ADC中的开关电容比较器。

图2 开关电容比较器电路图

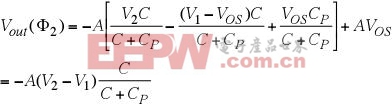

当图2中的开关φ1关闭时,输入失调存储在输入串联的电容C上,电容C将对比较器的输入失调电压VOS自动校零。电容CP表示比较器输入到地的寄生电容。在φ1相位周期结束时,C和CP上的电压为:

开关φ2关闭时,

如果CP小于C,那么上式可以简化如下:

因此电压V1和V2的差值通过比较器的增益得到放大,后面的锁存器根据比较器A的输出产生逻辑电平,输出Vout,直流输入失调电压自动校零。

评论