MPC8280多通道HDLC控制器的应用

程序员通过对SI RAM块编程来完成路由表的构建。每个SI包含2个SI RAM块,分别用于设计发送和接收的路由表,这样MPC8280内部的2个SI模块总共包含4个SI RAM块。每块由SI RAM构造的路由表包括256条表项,每条表项长度是2字节,每条表项最多可控制8个字节串行流数据的分配,所以1个SI模块支持的最长一帧的长度可达256×8×8=16 384比特。路由表表项的内容就是指定将TDM口上通过1~8个比特或字节的同步数据流分配给MCC、SCC、SMC、FCC等通信控制单元。最后一条表项必须激活路由表的结束标记,告诉TSA已处理完一帧,请等待下一个帧同步信号的到来。本文引用地址:https://www.eepw.com.cn/article/162451.htm

如图3所示,每块SI RAM(内含256条表项)等分为4个bank,即每个TDM口均各有1个bank一一对应;每个bank可以被程序员指派为对应不同的TDM口(但不允许将两个TDM口对应到同一个bank上)。这样,TDM口的串行数据流在指定bank的SI RAM表项的控制下被分别送往指定的通信控制单元进行处理。一个bank的长度可由设计人员自由设定(路由表有首尾标志),这是因为不同的应用,每一帧的比特数目并不一定相同;路由表即精确地确定了每一个TDM口帧流的比特数目。显然,一个帧流必须由多少条表项来处理也可以计算出来,即帧流总比特数/每表项处理的比特数。注意,路由表的表项数目必须是偶数,因此在编程时,如果的确是只有一条表项,那么就还必须再补上一条内容为空的表项。

此外,因为TDM口的接收、发送分别由2个SI RAM块实施控制,所以TDM口发送和接收的比特流的分配可以任意设计,甚至允许将不连续的比特流都分配到一个通信控制单元,也允许一个通信控制单元从某一个TDM接收,而从另一个TDM发送。

3 MCC的标准通道设计

一个MCC的数据是在特定SI控制的4个TDM口上传输;每个MCC可以支持128条时分复用通道(见图4),用来传输HDLC、透明通道,或7号信令通道数据。本文的设计是用MCC实现多通道HDLC通信协议。MCC的数据流可通过TSA的桥接直接送入MCC相应通道的FIFO处理。每个MCC可分解成4个子模块,每个子模块(包含32条通道)对应到1个TDM口上,即处理不同的物理TDM口的数据。MCC中的每个通道的工作模式均可独立设置,收发关系也可以独立映射;支持全局环回和基于单个通道的独立环回。

每个MCC中包含128个功能完全相同的通道,每个通道都有一套配置寄存器,这些寄存器功能相同,并依靠通道号进行索引寻址,进而初始化。

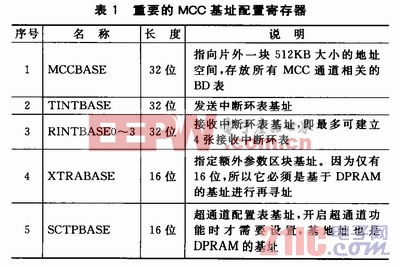

MCC的初始化遵循先全局、后通道的顺序。MCC的全局参数寄存器定位在DPRAM(bank 9)中,占用128字节,该寄存器组相对DPRAM基地址的偏移量为0x8800。在全局参数设置里比较重要的、将影响各通道配置寄存器空间寻址的地址索引寄存器如表1所列。

每个通道都有64字节的专用参数寄存器。采用“DPRAM基址+64×通道号”的方式计算出指定通道的专用参数寄存器组的基址。

每个通道还有8字节的额外参数寄存器,采用“DPRAM基址+8×通道号”的方式计算出指定通道的额外参数寄存器组的基址。该区块的主要内容包括:TBASE(16位,发送BD表首地址计算元素);RBASE(16位,接收BD表首地址计算元素)。

BD表通常放在片外内存中。1个MCC包含128条通道,每条通道都有自己的BD表,所有128条通道的BD表集中连续地存放在一个512 KB的段中。在这个空间内寻址某个通道对应的BD表的基地址的计算方法是:MCCBASE+8×RBASE(接收),MCCBASE+8×TBASE(发送)。接收和发送BD表都是一个环形队形,接收BD表至少须含2条表项,发送BD表至少须含1条表项。编程时,构造结构数组,可以把TBASE、RBASE设计成和通道号对应的数组索引。

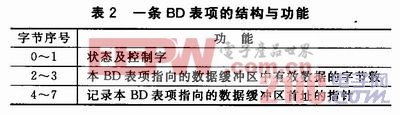

每条BD表项有8个字节,如表2所列。

环形队列结构的中断表也是放在片外内存中。发送中断对应一张表,基地址为TINTBASE;接收中断对应1~4张表,基地址分别为RINT-BASE0~RINTBASE3。中断表的长度完全由用户确定,但最少至少包括2条表项。每条中断表项长度为4字节,记录了中断表项是否有效、中断标志以及触发中断的通道号。

评论