基于nRF9E5的抗干扰跳频通信设计

在民用无线通信应用领域,由于人们对短距离无线通信系统的不断开发和广泛应用,免申请的ISM频段资源越来越紧张,各系统之间频率的重合机会也越来越大,系统干扰也越来越严重,所以设计具有跳频功能的民用抗干扰通信系统具有很直接的现实意义。利用该技术,既可以提高系统的抗干扰能力,也可以大大降低系统维护的复杂度。跳频通信系统主要由信号调制解调器、跳频图案发生器、频率合成器和跳频同步器等部件组成,本文主要介绍民用抗干扰慢跳频通信系统。

1 工作原理

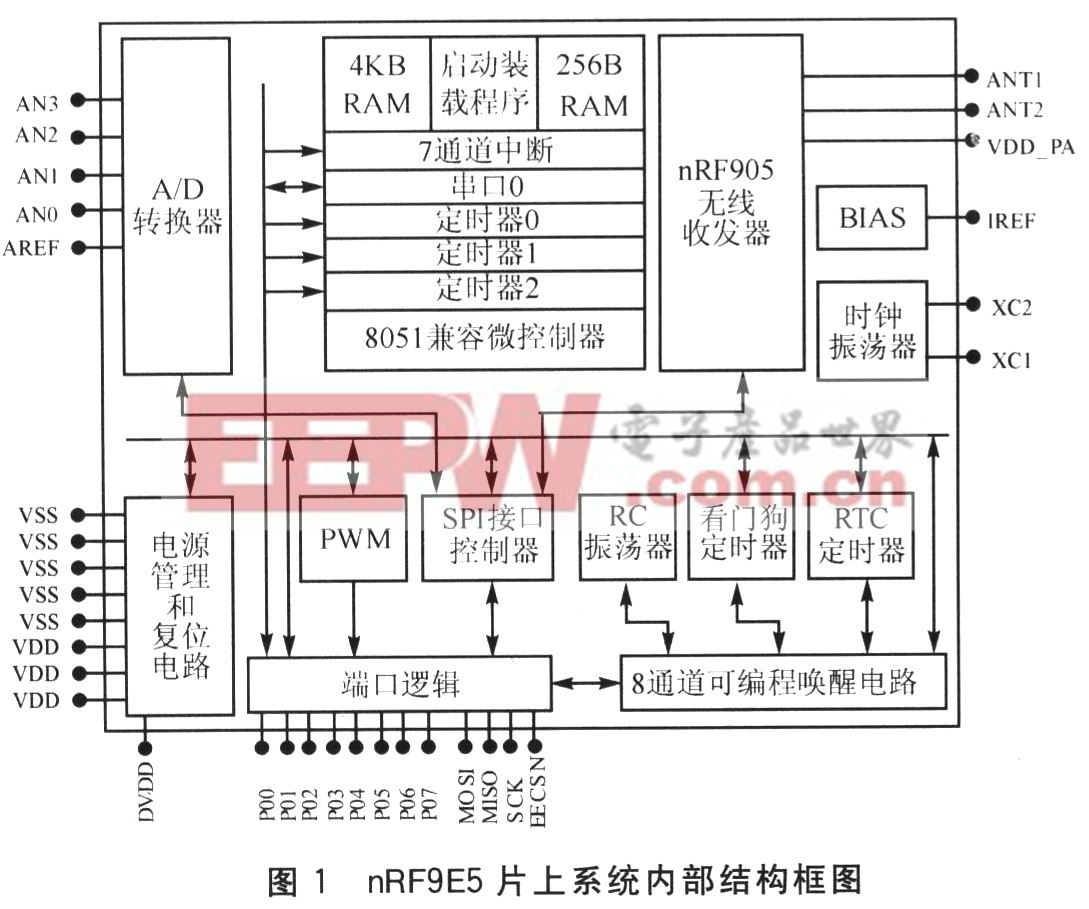

nRF9E5的内部结构如图l所示。片上系统集成的主要部件有:与8051兼容的微处理器、4 KB RAM及相关特殊功能寄存器(SFR)、4输入通道10位80 ksps的A/D转换器、433/868/915 MHz的nRF905无线收发器、电源管理及复位电路、PWM控制器、SPI接口控制器、低功耗模式RC振荡器、看门狗定时器、端口逻辑及RTC定时器,等等。微处理器与A/D转换器和无线收发器之间通过SPI接口进行连接,微处理器程序固化于外部的EEP―ROM存储器中,系统加电时由引导程序将固件通过SPI接口加载进片内的4 KB RAM区中,程序加载完毕之后系统由片内的RAM程序控制。该芯片射频信号输出功率可编程,最大输出为10 dBm,通道转换时间小于650μs,具有载波监听功能,支持LBT(Listen Before Trans―mit)协议。

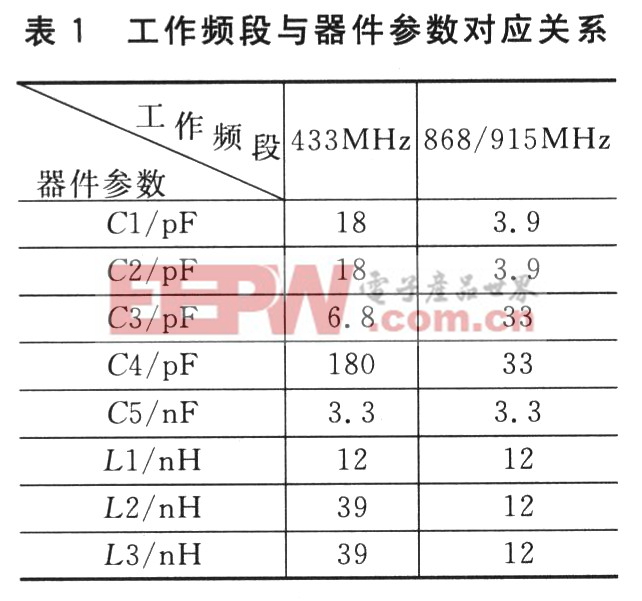

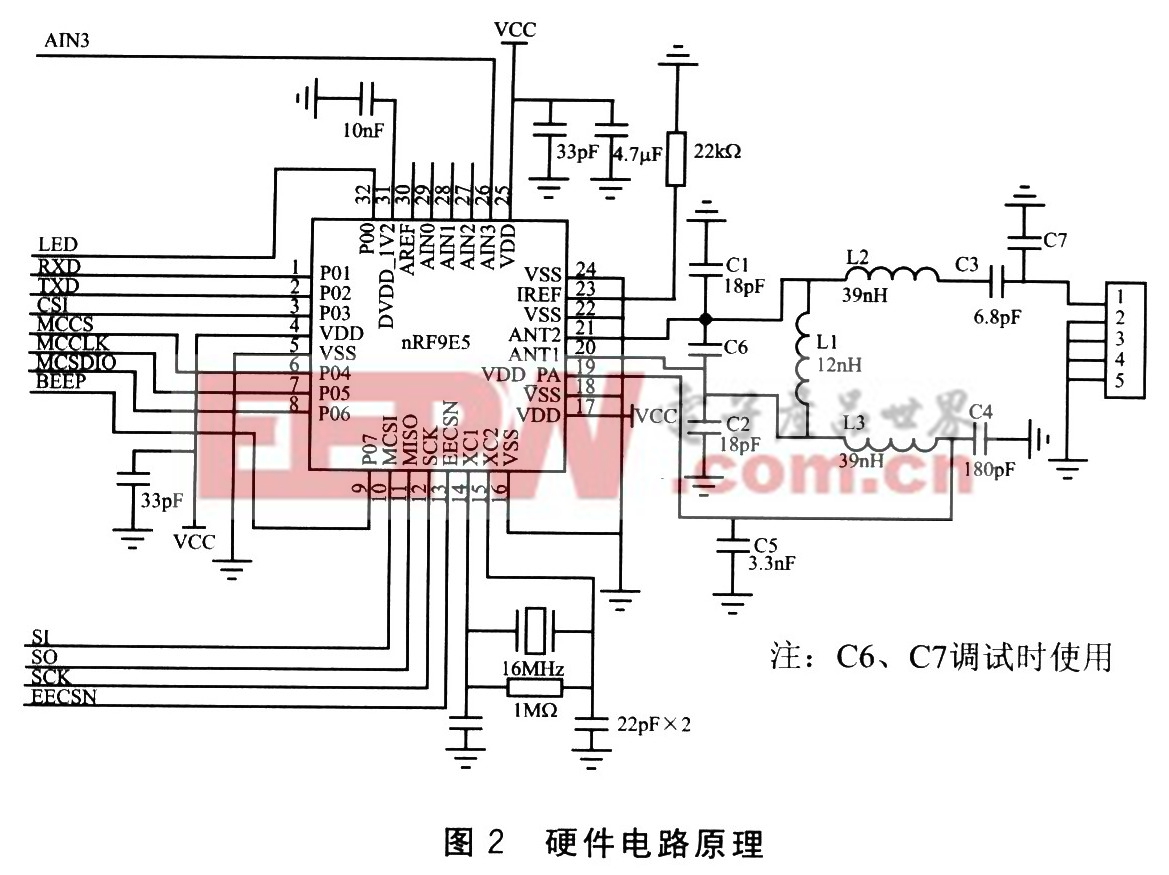

nRF9E5内部集成的无线收发器可工作于433/868/915 MHz频段范围内,具体的工作频段和频点由外围电路的阻容参数和相关寄存器数据决定。在图2所示的电路中,若系统要求工作于433 MHz频段,则相关器件按照表1第2列取值;若系统要求工作于868/915 MHz频段,则相关器件按照第3列取值。系统的工作频段不仅由硬件进行配置,而且还要在相应的RF配置寄存器中进行设置。其中HFREQ_PLL设置工作频段,CH_NO设置工作频点,HFREQ_PLL为一控制位,CH_N0为9位数据。具体的无线载波频率由下列公式进行计算:

fOP=[422.4+(CH_NO/10)]×(1+HFREQ_PLL)

式中fOP的单位为MHz。若HFREQ_PLL=O,系统工作于433 MHz频段,频点间隔100 kHz,频段范围为422.4~473.5 MHz;若HFREQ_PLL=1,系统工作于868/915MHz,频点间隔200 kHz,频段范围为844.8~947 MHz。由此可见,如果系统程序按照跳频图案产生的伪随机数设置CH_NO,则nRF9E5可以分别实现2个频段512个频点的抗干扰跳频通信。

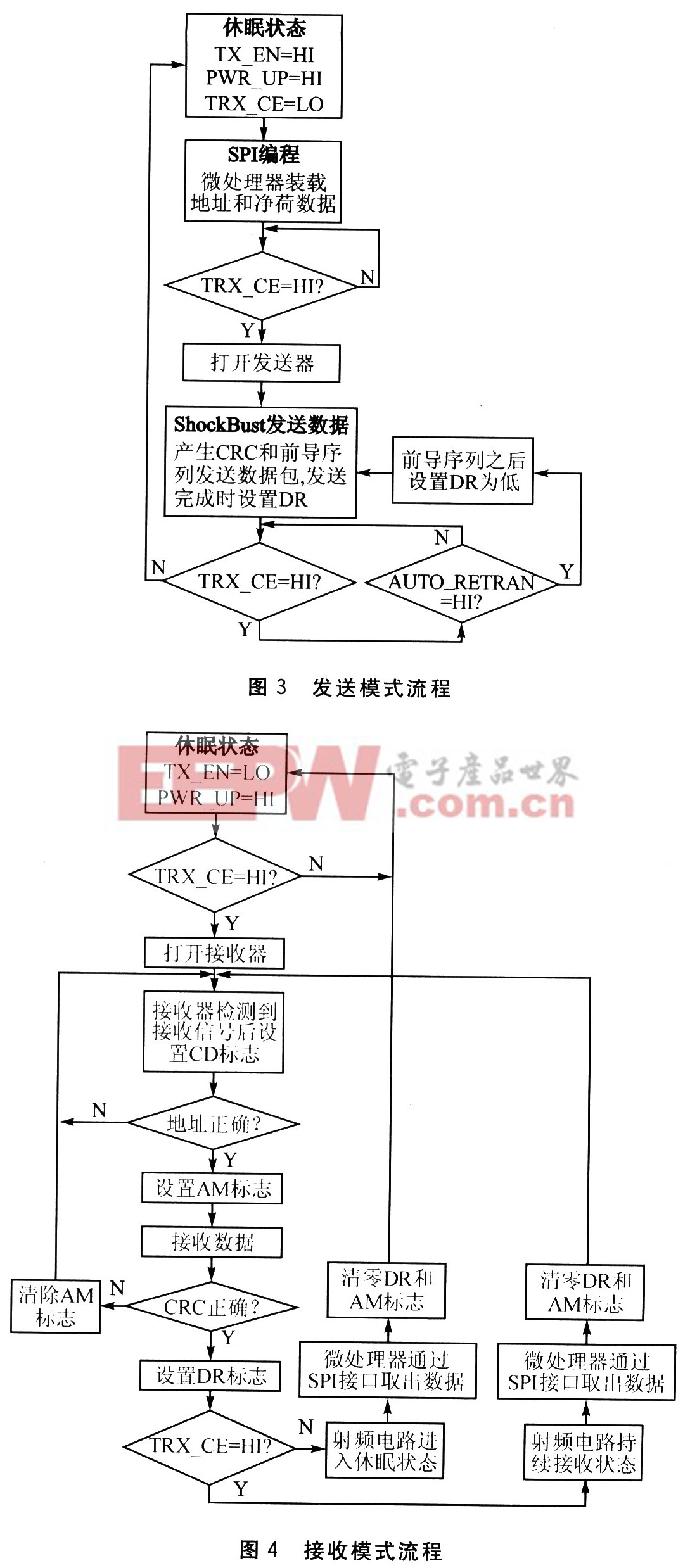

nRF9E5内部集成的无线收发器采用半双工的方式工作,工作方式由TRX_CE和TX_EN控制位决定,如表2所列。TRX_CE控制无线收发器处于休眠模式还是工作模式,当TRX_CE=l时,TX_EN决定无线收发器的接收和发送状态。无线收发器具有ShockBurst的特性,可实现高速的数据传输并在发送和接收模式之间快速转换,与射频数据相关的协议由片内nRF905收发器自动处理。nRF9E5只用简单的SPI接口与收发器进行数据传输。在ShockBurst接收方式下,当收到一个有效地址的射频数据包时,地址匹配寄存器位(AM)和数据准备好寄存器位(DR)通知片内MCU把数据读出。在ShockBurst发送方式下,nRF905自动给要发送的数据加上前缀和CRC校验。当数据发送完后,数据准备好寄存器位(DR)会通知MCU数据已经处理完毕。具体的收发流程如图3和图4所示。

评论