基于SOPC的DDS信号发生器设计

1. 2 D/ A 转换器

从DDS 核输出的是一个数字信号,需要将数字信号转换成模拟信号,才能便于观察。DAC 有电压和电流输出两种,其输出的信号并不能真正连续可变,而是以其绝对分辨率为最小单位,所以它的输出实际上是一个阶梯模拟信号,所以需要将D/ A 输出的信号通过低通滤波器平滑后得到纯净的模拟信号。在该设计中用到型号为AD9742 的D/ A 转换器,AD9742 是具有12 位、低功耗、转换速度可达到100 Mb/ s 的D/ A 转换器。

1. 3 基于SOPC 的硬件架构

系统开发包括硬件部分和软件部分,而硬件部分是由SOPC 开发工具搭建而成。SOPC Builder 生成NIOS 嵌入式处理器,NIOS 嵌入式处理器开发工具允许用户配置多个CPU ,在标准库中添加外围电路,也可以由用户自定义外设,综合处理自定义系统,这样使设计变得更加灵活。

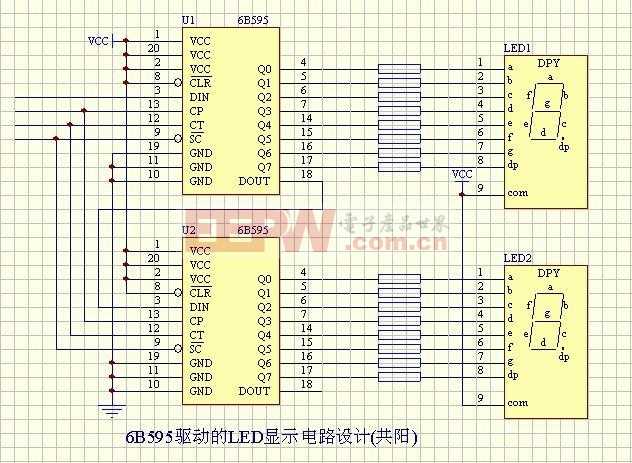

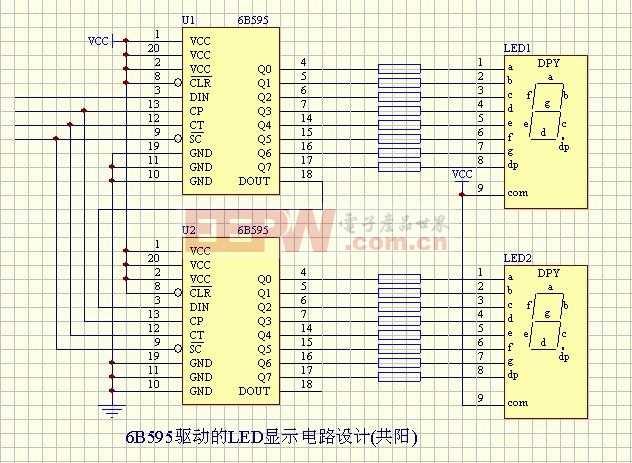

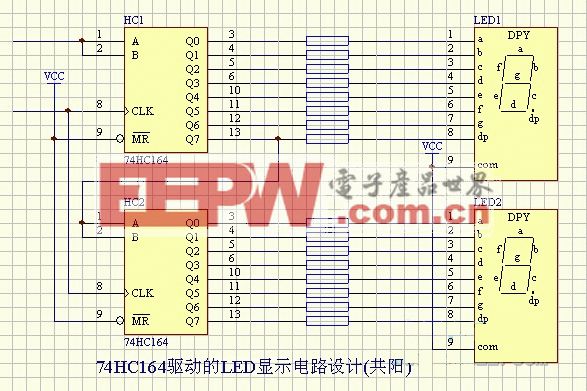

打开SOPC Builder 后分别添加CPU,PIO 输入( 10 个按键用作频率字的输入、1 个按键用作确认、4 个按键用作波形的选择) ,存储器( FLASH,SRAM 和SDRAM) ,PIO 输出( 10 位作为ROM 的地址、2 位作为ROM 块的选择、7 位为LED 段码、1 位为LED 的选通端) 和定时器。所有组件添加完后的硬件架构图如图3 所示。

图3 SOPC 硬件架构图

SOPC Builder 生成之后,在Quartus 软件中可以添加生成之后的CPU 模块,而DDS 模块是用VHDL 语言编写而成,DDS 模块图如图4 所示。其中的ROM 大小为12 1 024,共设置4 块ROM 分别存储正弦波、方波、三角波、锯齿波。波形数据是由Mat lab软件计算出来的,并将数据以. mif 文件格式存储。累加器的输出为波形存储器的地址,进行波形的相位 幅值转换后,作为输出的波形的幅值。10 位的寻址ROM 相当于将一个周期的信号进行离散化,形成具有1 024 个样值的序列。累加器产生的地址通过波形的地址分配读取不同存储器中的数据,然后将读出来的数据经过D/ A 转换器,转换成模拟信号输出。

图4 DDS 模块图

2 软件设计

NIOS 完整的开发环境是NIOS 处理器与用户的接口界面。使用NIOS IDE 可以完成所有的软件开发任务,包括程序的编辑,编译和调试。硬件提取层( HAL) 支持通用I/ O 器件,可以通过编写标准C 程序访问硬件,HA L 减少了对硬件寄存器的访问,直接与外围器件进行通信或控制。不同的外围硬件需要不同程度的HAL 的支持,需要运行HAL 的软件驱动器。DDS 系统控制在NIOS IDE 环境下用标准C 语言实现,通过编写代码、编译、链接、调试、下载几个步骤完成整个设计。

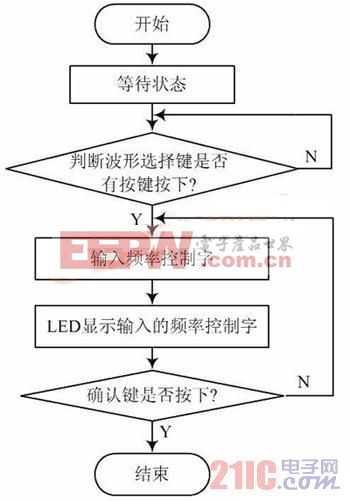

打开IDE 开发环境后,第一步需要做的就是新建一个工程,将SOPC Builder 生成的. ptf 添加之后,系统根据该硬件的地址分配情况自动生成相应的头文件,该头文件定义了各个组件的基地址。当SOPC 系统发生变化,IDE 将在用户编译和运行应用程序时重新对HAL 进行编译。整个软件编写的流程图如图5 所示。

图5 软件流程图

3 系统调试过程与结果

评论