USB 3.0中的CRC校验原理及实现

(3)发送端对输入的数据作除法运算后,将所得到的余数按位取反,取反后的余数放在待发送数据的高位,组成了新的数据流。接收端CRC校验采用与CRC产生相同的算法来实现,只是作为输入数据的是原始的被除数数据和对应的CRC校验码组成的新数据流。如果接收端的余数与(2)的要求一致,则说明接收端准确无误地接收到了数据。

2 并行CRC校验的设计

在USB 3.0协议中,数据最高传输速率高达5 Gb/s,串行方法无法满足实时性要求。本文中,CRC校验采用的是并行设计方法。

在USB 3.0协议中,数据收发是以字节为单位来传输的,所以在发送端和接收端可以通过一个8位移位寄存器将串行数据转换成字节表示形式,然后再对数据进行并行的CRC码产生和校验。本文引用地址:https://www.eepw.com.cn/article/155417.htm

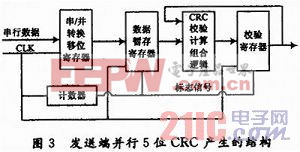

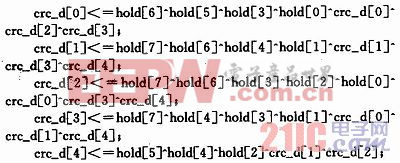

以链接控制字中的5位CRC为例,发送端并行CRC产生的设计结构如图3所示。计数器用于产生标志信号,计数值为8时串并转换结束。数据暂存寄存器获取字节数据,经组合逻辑计算后产生新的校验寄存器值。并行CRC5的余数多项式表达式如下:

在接收端,按照和发送端同样的电路,对发送端产生的CRC校验码和输入的数据一并进行CRC校验,如果接收端成功接收,最后得到的CRC校验码为常数(01100)。

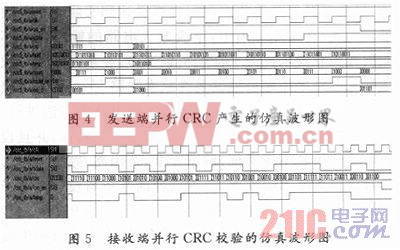

3 仿真结果

发送端和接收端的并行CRC产生和校验设计用Verilog HDL实现,用ModelSim工具进行仿真,发送端并行CRC产生和接收端CRC校验的仿真波形分别如图4和图5所示。在发送端,每输入8个数进行一个并行的CRC5计算,crc_d寄存器的值随发送的数不断更新,直到最后产生一个余数,在接收端将该余数和发送端的数一并进行CRC5校验,最后CRC得到一个常数值01100。

4 结语

虽然并行方法在电路规模上比申行算法大,但是能够在单位时间内完成更多位数据的校验,可以有效降低电路的工作频率,硬件实现也较容易。USB 3.0数据的最高传输速率高达5 Gb/s,采用并行CRC校验设计完成USB 3.0数据传输中CRC码的产生和校验。可使高速USB串行接口引擎电路方便地与UTMI接口。

评论