远程无噪传送高速ADC数据

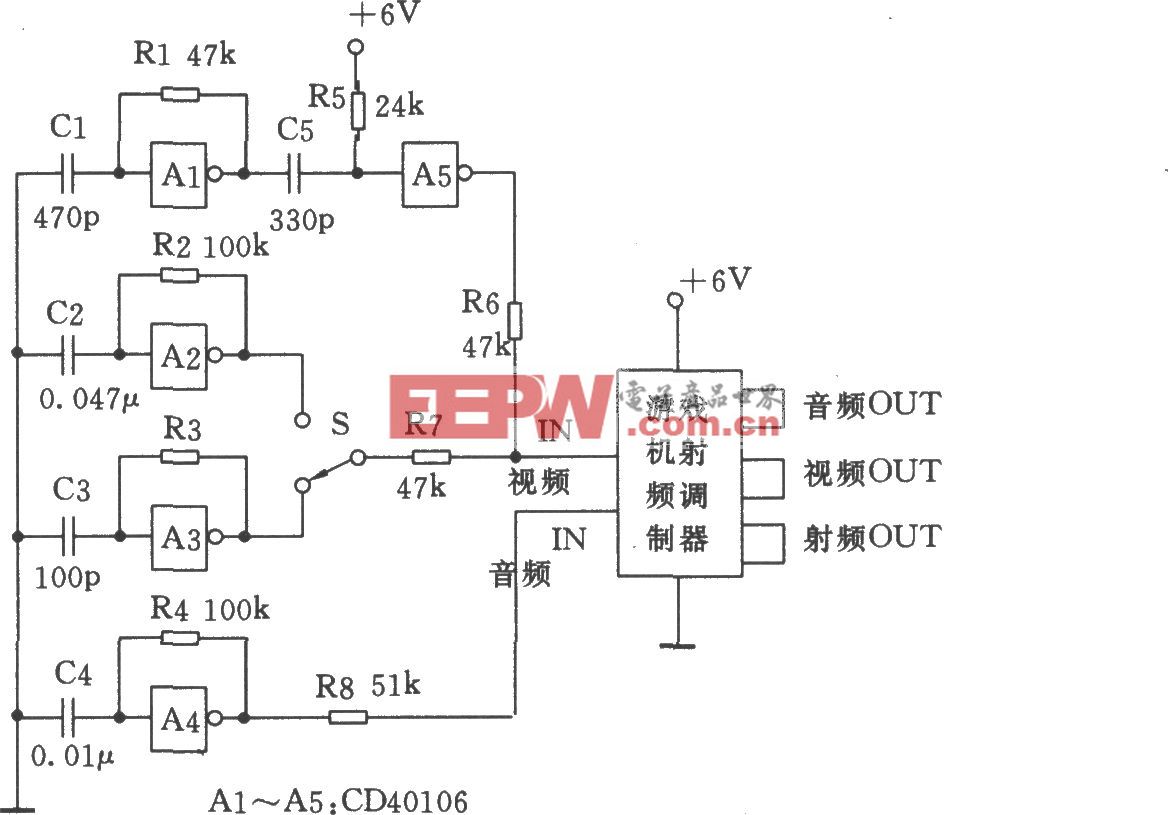

解决问题的一种办法是采用LVDS(低电压差分信号)数据总线。图1示出带LVDS输出的ADC框图,驱动一个ASIC或解串器。此处ADC以LVDC信号格式输出串行数据流。在接收端,LVDS就绪ASIC或解串器恢复N位输出。

在上电时序期间,ADC和接收器处理完2步初始化时序。初始化与包含在每个芯片上的PLL同步有关。首先,接收器锁定到振荡器频率。ADC PLL锁定到CLKIN。在此之后,ADC送出称之为‘SYNC’图形的数据时序。这是任意“1”随后相同“0”数的图形,定时在输出数据率。接收器中的PLL锁定到SYNC图形,并发送‘LOCK’信号返回到ADC。此信令ADC接收器被锁定,并为输入数据准备好。输出数据由‘起始位’(总是‘1’)、n位数据和‘停止位’(总是‘0’)组成。图2示出时序流程图。

因此,FRAME由n+2位组成。数据流频率为(n+2)x fsample。只要接收器的PLL保持锁定,接收器就可保持接收数据。若锁定去除,则LOCK线置为低态,而同步图形再次请求ADC。

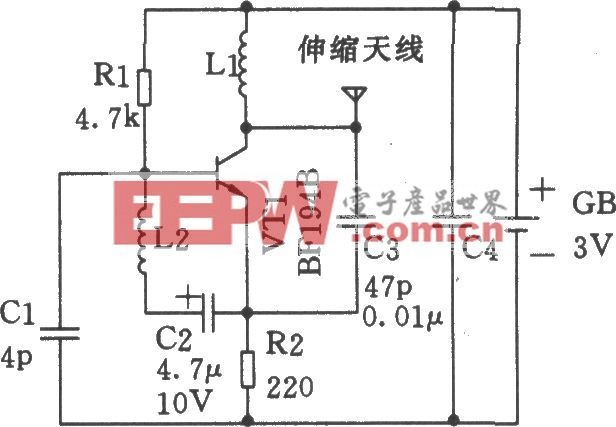

ADC输出驱动器是电流源,具有驱动100Ω双绞线、PCB迹线或微带线的能力。图3示出靠近接收器的两个典型终端电路。图3a示出一个简单的终端电路,电阻器端接ADC线以降低可能发生的任何反射。它也提供产生输出信号所需的电流源负载。图3b也是一个简单的终端电路,它提供缓冲缆线的共模电阻。除ADC和解串器之间连线数最少外,差分信号格式保持磁场紧紧地包围在传输线周围。这降低了连线的EMI。■ (冰)

评论