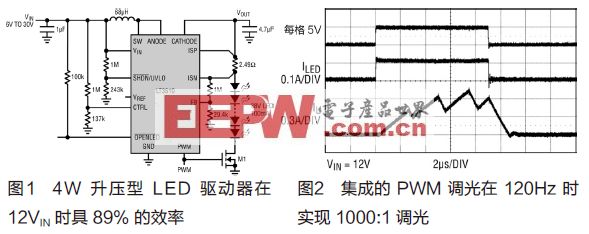

粒子探测器读出电路数字滤波器设计

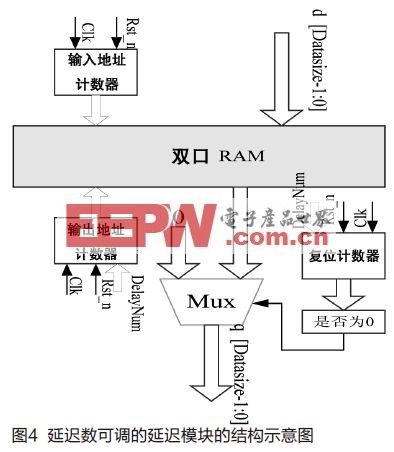

—— 实现了延迟单元数可调的延迟模块的设计

H4(z)的实现结构

对于模块H4(z),它包括了一个比例因子,积分器单元和一个延迟单元,它的结构很简单,可以采用如()1Hz同样的结构,即直接Ⅱ型的转置形式,这样可以把积分器和延迟单元放入同一个结构,可以减少一个延迟单元;另外可以调整滤波器增益G的值使得比例因子Gk的值为2-n,这样,可以通过数据转换的方法来实现除法,例如,如果积分器的输出是20位,而通过数据转换只取其高14位作为滤波器的输出,那么就相当于除以64了,这样就不需要除法器或者是乘法器这样的运算单元来实现了,而且这只是改变了滤波器的增益,对滤波器的性能没有影响。

实验结果

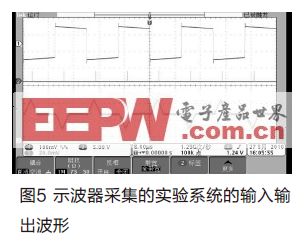

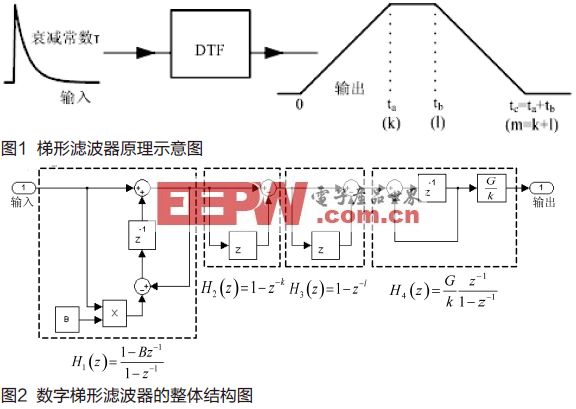

本文所介绍的数字梯形滤波器设计经过FPGA验证,实现了正确的功能。图5是实际测量得到的输入输出波形图,图中上方波形是前级模拟放大器的输出波形,它经过ADC量化后

图5 示波器采集的实验系统的输入输出波形输入数字滤波器,下方的波形即是经过本文设计处理后输出梯形滤波结果再由DAC恢复出的模拟波形。

结语

本文实现了数字谱仪系统中常用的梯形滤波算法的结构设计,通过采用最佳滤波器结构以减小所需要的运算单元和延迟单元,并保证其在有限精度运算时性能不受到影响。通过采用延迟数可调的延迟单元模块,可以改变梯形滤波器上升时间和平顶时间的宽度,以适应不同的噪声环境,最后通过FPGA验证了数字梯形滤波器结构设计的正确性。

评论