基于AD9640的无线接收机设计

接收机排版布线

本文引用地址:https://www.eepw.com.cn/article/105939.htm本设计中,接收机布线坚持2W原则:布线宽度为W,线间距不小于2W。PCB电路板分为模拟层和数字层两个部分,共12层,制版安排见图2,布线安排设计如下。

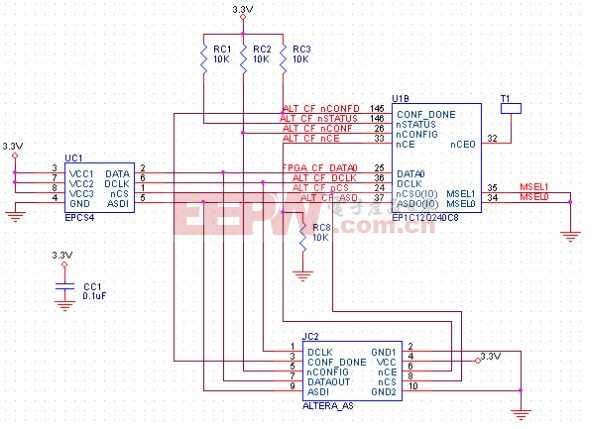

(1)模/数布线和元件排版分离。高速信号位于优质布线层clk-digital component和signal_1,高速信号线同低速信号线尽量远离,重要的低速信号线位于低速信号层signal_2 和signal_3。首先,保证关键高速时钟和信号线布放于层clk-digital component和signal_1;然后保证关键低速信号线位于层signal_2 和signal_3;其次,低速信号线进入高速布线层clk-digital component时应该远离高速信号线(尤其是时钟),高速信号线进入低速布线层signal_2 和signal_3应该远离低速信号线;最后,上述原则无法实施时应该增加布线层。

(2)PCB板下三层为模拟电路,上七层为数字电路;层clk-digital component布线64MHz时钟;层signal_1布线64MHz数字信号,包括AD9640采样64MHz高速数字信号;层signal_2 和signal_3布线小于64MHz的所有其它数字信号;将数字地GNDdigital2用多个过孔连接到GNDdigital1上,GNDdigital2仅仅为隔离模数两个系统,保护模拟信号免受数字干扰。GNDdigital1作为电源+5V的数字地;GNDdigital2作为+1.8V、+2.5V、+3.3V的数字地。

(3)FPGA、稳压片等所有核心元件位于顶层clk-digital component。

(4)各层敷铜接地方法:

● 层clk-digital component、signal_1、signal_2 、signal_3的大面积敷铜,并通过多个过孔连接到GNDdigital1;

● 层analog component的大面积敷铜,并通过多个过孔连接到GND analog。

(5)电源布线:电源线根据使用区域大面积填充,形成分割的电源平面。模拟电源平面PWRanalog分割为3.3V和5V两个部分,数字电源平面PWRdigital分割为1.8V、2.5V、3.3V、5V四个部分。

实物制造及测试

图4示出所设计的接收机实物图,将其放置在一定的温度、湿度和振动压力之下测试以检查任何设计或工作的缺陷。

评论