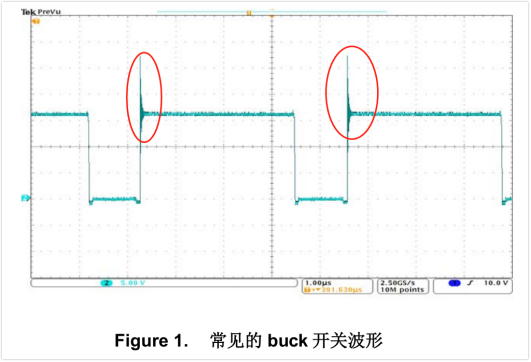

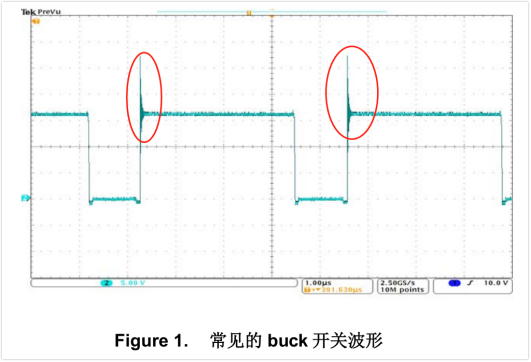

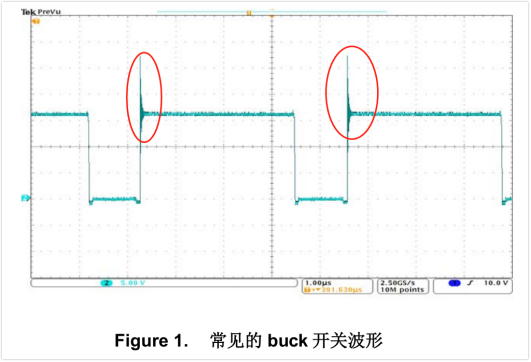

本应用报告首先给出了降压式开关电路(buck)在上管开通瞬间的的一个等效谐振回路模型。根据该模型推导出使得开关振铃最小化的阻容缓冲电路(snubber)的参数计算公式,并结合参数公式给出了一套 snubber 电路的快速设计方法,最后以 LM5119 的 EVM 为例给出了 snubber的设计过程和结果。1、Buck 电路中snubber 的引入和参数计算1.1、Snubber 电路的引入由于寄生参数的存在,开关电源电路在开关动作瞬间会产生开关振铃。Figure 1 为 buck 电路开关节点(两个开关与电感交汇点)的典型波形,可见在上管开通瞬间都有不同程度的振铃。

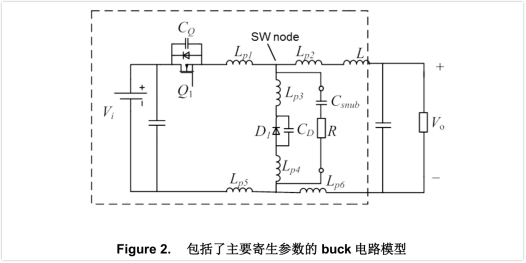

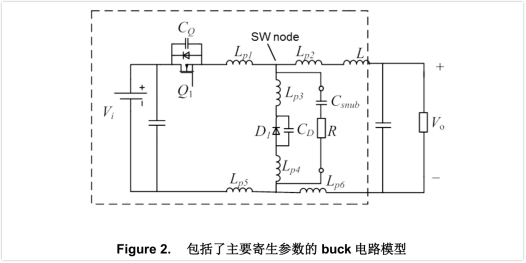

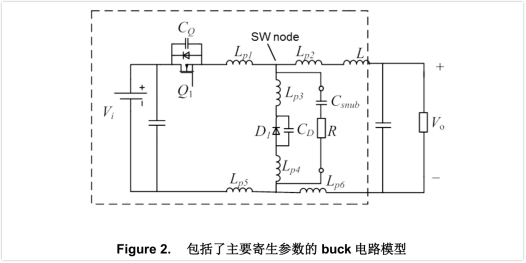

振铃的存在,可能使得开关管承受的电压超过其耐压值而发生击穿;另一方面,开关振铃为远超开关频率的高频振铃,并伴随很高的 dV/dt,会带来传导和辐射的 EMI 问题,可能会使得终端产品不能通过 EMI 标准测试,更严重时甚至会干扰开关电源自身的信号电路或临近的其他功能电路的正常工作。所以尽可能地抑制开关振铃是开关电源设计中一个很重要的环节。常见的措施,包括布线的优化减小线路寄生参数;选用二极管反向特性好的器件;降低开关速度;在振铃回路中放置 snubber 等。其中,snubber 是最为常用的手段,特别是在以上其他措施因客观因素的限制而不能达到最佳效果时。Snubber 不仅能改变振铃频率,同时其电容效应会降低开关节点的 dV/dt,从而有效抑制 EMI。本文以 LM5119 为实例讨论buck 电路的 snubber 的相关问题,但同样的设计思路和方法可以推导到其他非隔离拓扑中。1.2、包含寄生参数的振铃回路等效Figure 2 展示了包含主要寄生电感和电容的 buck 电路,RC snubber(R 和 Csnub)放置在开关节点和GND 节点之间。该电路主要用来抑制上管开通瞬间的振铃,而该振铃正是绝大多数过压问题和 EMI 问题的源泉。

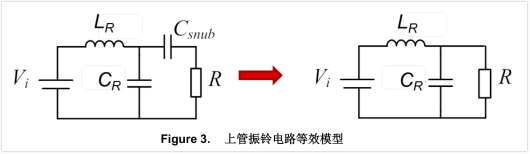

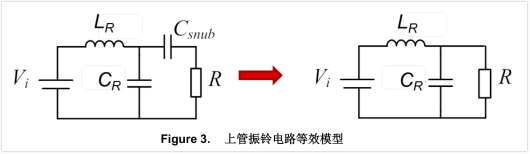

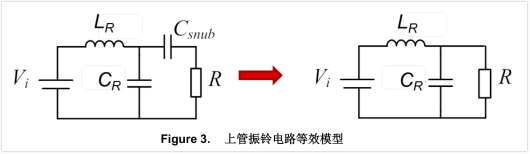

首先由于开关过程在极短时间(从数个纳秒至数十个纳秒)完成,在此过程中电感 L 的电流几乎不变,故 L 和 Lp2(包括串联的 Lp6)不参与振铃。其次,在振铃使得幅值超过 Vi后,上管 MOSFET 的沟道已完全打开,CQ被短路,也不参与振铃。故最终的振铃回路由图 3 左虚线方框中电路组成。该电路可等效成图 3 中 LC 谐振电路,新的 LR和 CR为 Lp1、Lp5,Lp3, Lp4, CD等所有参与振铃的寄生感容的复合值。通常 Snubber 的 Csnub取值在数 nF 以上,在振铃频率 fR(加了 snubber 后)下的阻抗很小。以Csnub=2.2nF, fR=150MHz 为例,阻抗为 1/(j*2πfR*Csnub)=-0.48jΩ。而 R 一般在数欧姆以上,故 figure 3左可进一步近似等效为 figure 3 右。

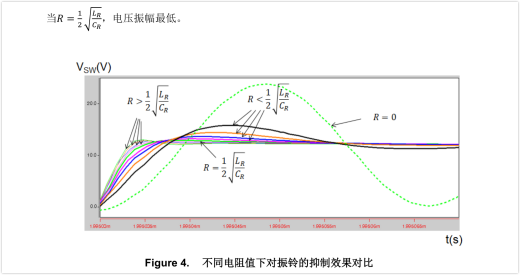

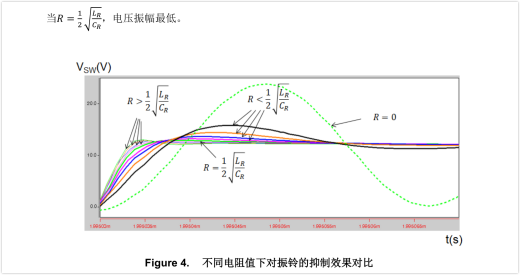

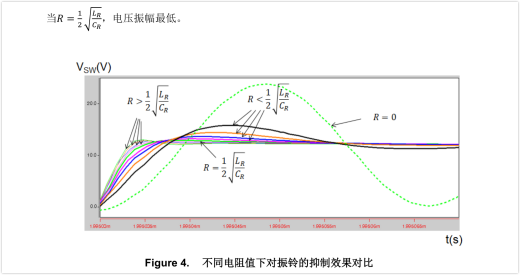

1.3、等效模型下的 snubber 参数计算由 figure 3 电路,可得到:故为使电路电路为阻尼振铃,R 的取值为:Figure 4 给出了不同电阻值的仿真对比。仿真条件为:Lp1=Lp5=10nH,Lp3=Lp4=2nH, Csnub=10nF,CD=200pF

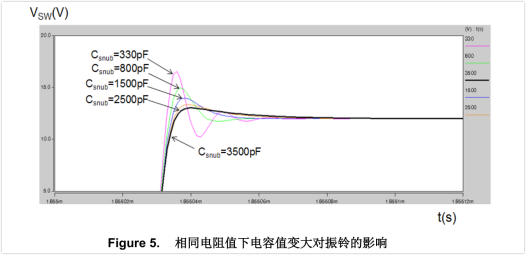

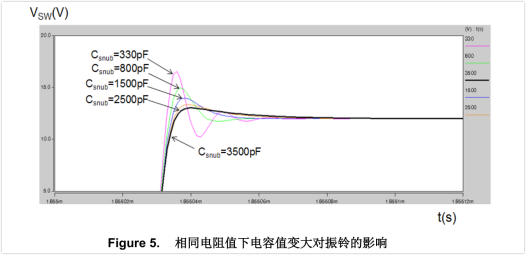

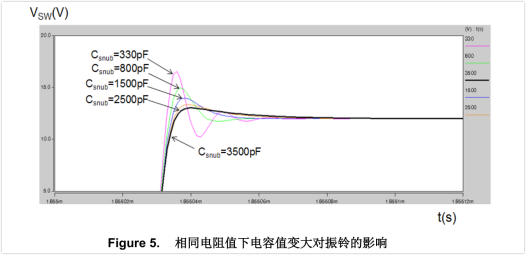

同时,Csnub越大,在 RC snubber并联到CR后,实际等效的 CR会更大,意味着同样的阻尼电阻对振铃抑制效果越好。Figure 5 给出了在相同 R(R=2.2Ohm,其他电路寄生参数如前文)下,不同 Csnub的仿真结果。电容越大,抑制振铃振幅效果越好。而且当电容达到一定程度大小以后,电容的增加给振铃抑制的效果并不显著,比如图 x 中 2500pF 和 3500pF 对应的振幅对比。究其原因,在 RCsnubber 支路,电路电抗为 R+1/(j*2πfR*Csnub),当 C 达到使得 1/(j*2πfR*Csnub)<<R 时,此后 C 的进一步增大对电路几乎忽略不计。

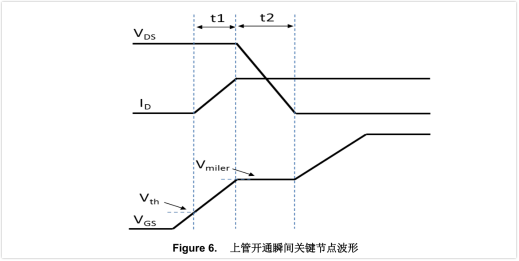

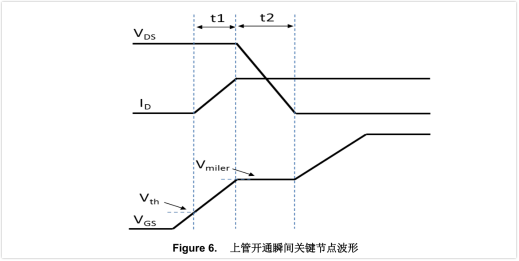

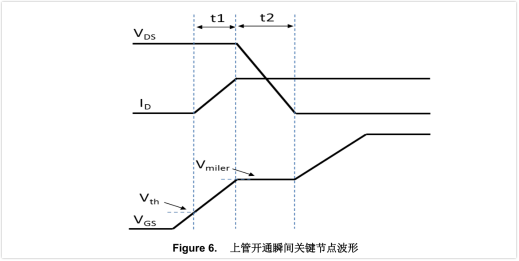

另一个不能忽略的方面是,Csnub越大,buck 电路的损耗会越大,效率会越差。损耗包括两个方面。式(3)为 snubber 电阻上的损耗,可知该损耗正比于电容容值。Figure 6 为上管开通瞬间的驱动电压和MOSFET 上电流电压对应关系。

式(4)为 MOSFET 开关损耗(包括开通和关断损耗,并假设开通关断时间一致),因为其中 t2 随 Csnub的增大而增大,开关损耗也随之增大。可见,从较小损耗的角度,电容越小越好。设计者需要在控制功耗和抑制振铃之间找到较好的平衡。

2、一种实用快捷的 snubber 设计方法2.1、设计步骤根据以上的讨论,下文给出一个基于上文讨论等效模型的实用快捷的缓冲电路设计方法。第一步,需要确定图 figure 3 中的 LR和 CR。首先测量初始振铃频率。然后在 snubber 将要放置的位置上,放置一个 Cadd,如图 7 所示,因此新的可测得的振铃频率表达式为:以上两式中,仅 LR和 CR为未知量,故可通过两式联立,解得 LR和 CR.

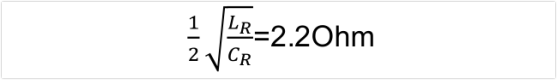

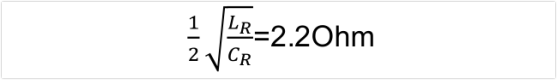

第二步,选取合适的 R 值使得 R 值近似于:

注意,电阻的封装应考虑散热。使得电阻功率等级大于电阻上损耗。电阻损耗表达式为,

第三步,选择合适的电容值 Csnub。如前文所说,电容值的选择是振幅抑制和控制损耗的折中。可选择以式(11)作为起点,根据损耗情况和振幅抑制效果,进行进一步的调整:增大电容抑制振幅,减小电容提高效率。

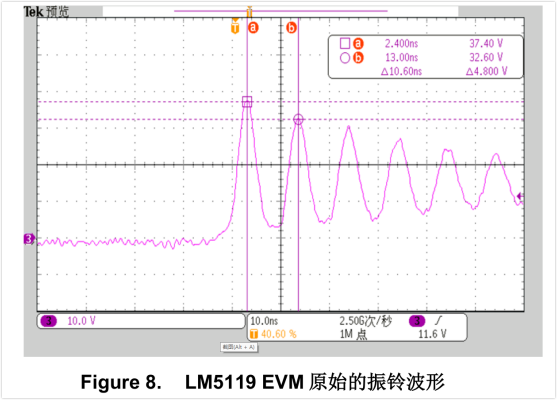

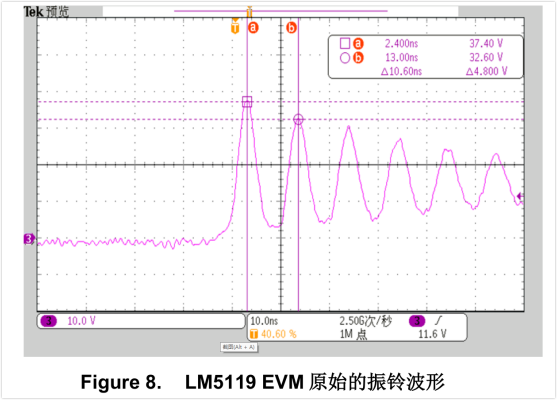

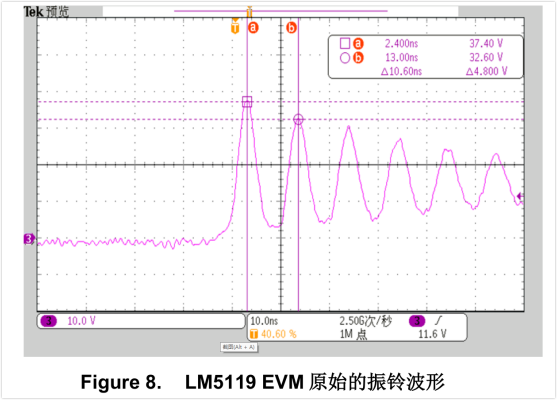

2.2、LM5119 EVM 缓冲电路设计实例以 LM5119 EVM 为例,测试条件为 VIN=16V, VOUT=10V, IOUT=1A。第一步,通过示波器读出开关上升沿波形,如 figure 8。可知,f1=93MHz。

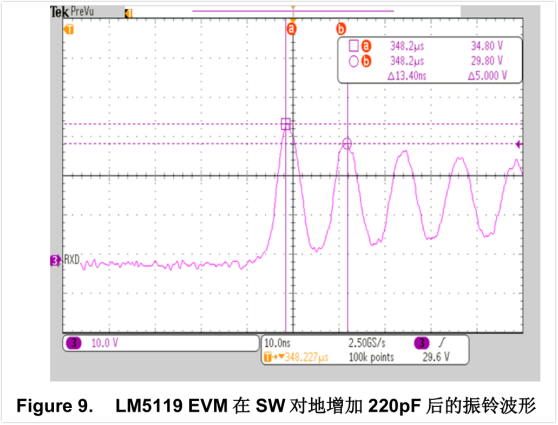

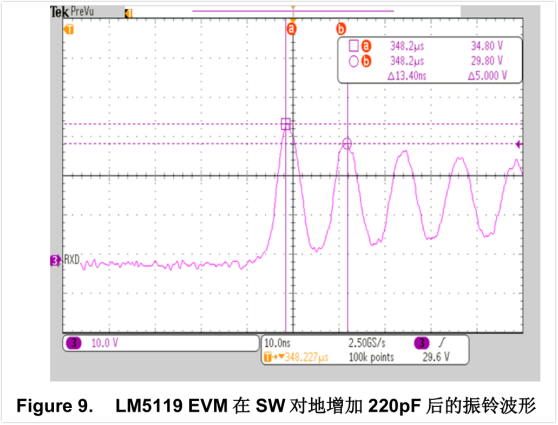

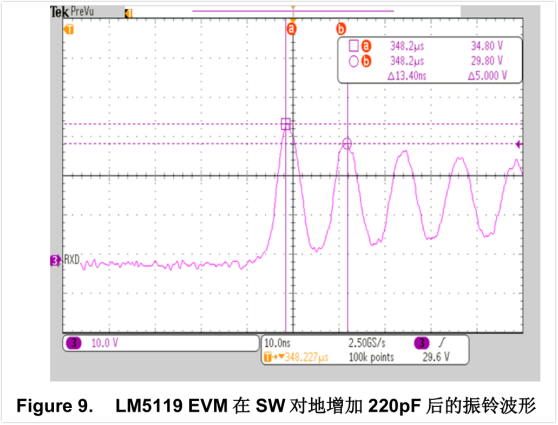

在 EVM 原有的空置的snubber 位置上增加一个新的 220pF 的电容后。新的波形如 figure 9,f2=75MHz。故可解得 LR=7.5nH,CR=387pF。

由式(9)得:

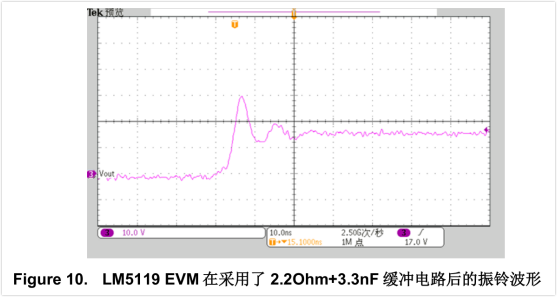

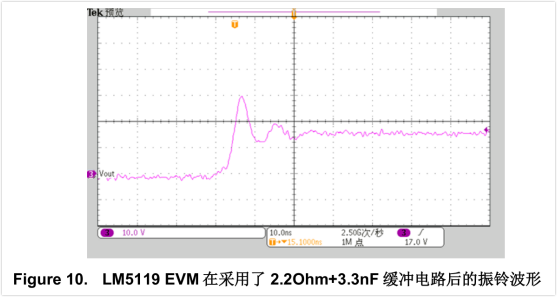

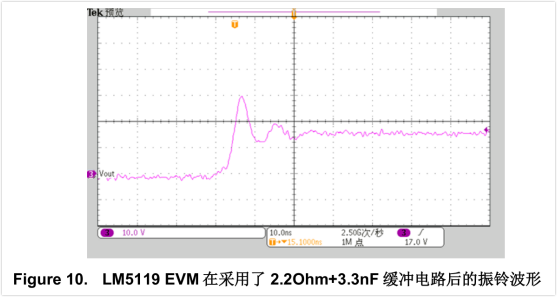

故可取 R=2.2 欧姆再由式(11)。选择接近的 Csnub=3.3nF。最后得到的振铃波形如 figure 10 所示,可见振铃幅度大大减弱。另外,值得注意的是,该实验结果效果比仿真结果略差。主要原因是 snubber 本身也会导入寄生电感,削弱了 snubber 的效果。因此在实际的操作中,snubber 电路需要尽量选择高频特性好的电阻电容。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。