- 一.TTL TTL集成电路的主要型式为晶体管-晶体管逻辑门(transistor-transistor logic gate),TTL大部分都采用5V电源。 1.输出高电平Uoh和输出低电平Uol Uoh≥2.4V,Uol≤0.4V 2.输入高电平和输入低电平 Uih≥2.0V,Uil≤0.8V 二.CMOS CMOS电路是电压控制器件,输入电阻极大,对于干扰信号十分敏感,因此不用的输入端不应开路,接到地或者电源上。CMOS电路的优点是噪声容限较宽,静态功耗很小。

- 关键字:

TTL CMOS

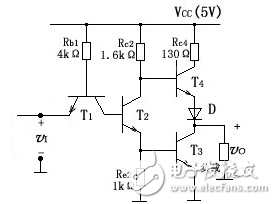

- 随着数字电路向高集成度、高性能、高速度、低工作电压、低功耗等方向发展,数字电路中的△I噪声正逐步成为数字系统的主要噪声源之一,因此研究△I噪声的产生过程与基本特点,对认识△I噪声特性进而抑制△I噪声具有实际意义。 反相器是数字设计的核心。本文从反相器入手,分析了TTL和CMOS中△I噪声的产生过程与基本特点。 1 △I噪声的产生 1.1 TTL中△I噪声的产生 TTL反相器的基本电路如图1所示。在稳定状态下,输出Vo分别为高电平VOH和低电平VOL时,电源提供的电流IH和I

- 关键字:

TTL CMOS

- [问]:

1、电阻电容的封装形式如何选择,有没有什么原则?比如,同样是 104 的电容有 0603、0805 的封装,同样是 10uF 电容有 3216、0805、3528 等封装形式,选择哪种封装形式比较合适呢?

2、有时候两个芯片的引脚(如芯片A 的引脚 1,芯片B 的引脚 2)可以直接相连,有时候引脚之间(如A-1 和 B-2)之间却要加上一片电阻,如 22欧,请问这是为什么?这个电阻有什么作用?电阻阻值如何选择?

3、藕合电容如何布置?有什么原则?是不是每个电源引脚布置一片

- 关键字:

封装 TTL

- 本文主要介绍了什么是负电压及如何产生,希望对您的学习有所帮助。

1、电荷泵提供负压

TTL电平/232电平转换芯片(如,MAX232,MAX3391等)是最典型的电荷泵器件可以输出较低功率的负压。但有些LCD要求-24V的负偏压,则需要另外想办法。可用一片max232为LCD模块提供负偏压。TTL-in接高电平,RS232-out串一个10K的电位器接到LCM的VEE。这样不但可以显示, 而且对比度也可调。 MAX232是+5V供电的双路RS-232驱动器,芯片的内部还包含了+5V及&pl

- 关键字:

负电压 TTL

- 本文介绍了上下拉电阻的作用、使用方法等问题。

重要信号线的上下拉问题

一般说来,不光是重要的信号线,只要信号在一段时间内可能出于无驱动状态,就需要处理。

比如说,一个CMOS门的输入端阻抗很高,没有处理,在悬空状况下很容易捡拾到干扰,如果能量足够甚至会导致击穿或者闩锁,导致器件失效。祈祷输入的保护二极管安全工作吧。如果电平一直处于中间态,那输出就可能是不确定的情况,也可能是上下MOS都导通,对器件寿命造成影响。

总线上当所有的器件都处于高阻态时也容易有干扰出现。因为这时读写控制

- 关键字:

CMOS TTL

- 现在常用的电平标准有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,还有一些速度比较高的LVDS、GTL、PGTL、CML、HSTL、SSTL等。下面简单介绍一下各自的供电电源、电平标准以及使用注意事项。

TTL:Transistor-Transistor Logic 三极管结构。

Vcc:5V;VOH>=2.4V;VOL<=0.5V;VIH>=2V;VIL<=0.8V。

因为2.4V与5V之间还有很大空闲

- 关键字:

TTL,CMOS

- 简介:CMOS和TTL集成门电路在实际使用时经常遇到这样一个问题,即输入端有多余的,如何正确处理这些多余的输入端才能使电路正常而稳定的工作?本文给出了解决这个问题的方法,供大家参考。

CMOS门电路

CMOS门电路一般是由MOS管构成,由于MOS管的栅极和其它各极间有绝缘层相隔,在直流状态下,栅极无电流,所以静态时栅极不取电流,输入电平与外接电阻无关。由于MOS管在电路中是一压控元件,基于这一特点,输入端信号易受外界干扰,所以在使用CMOS门电路时输入端特别注意不能悬空。在使用时应采用以下

- 关键字:

CMOS TTL

- 简介:本文介绍了TTL电平和CMOS电平之间的区别以及使用注意事项等内容。

TTL:双极型器件,一般电源电压 5V,速度快(数ns),功耗大(mA级),负载力大,不用端多数不用处理。

CMOS:单级器件,一般电源电压 15V,速度慢(几百ns),功耗低,省电(uA级),负载力小,不用端必须处理。

CMOS 和 TTL 电平的主要区别在于输入转换电平。

CMOS:它的转换电平是电源电压的 1/2,因为 CMOS 的输入时互补的,保证了转换电平是电源电压的 1/2。

TTL:

- 关键字:

TTL CMOS

- 一、CMOS门电路

CMOS 门电路一般是由MOS管构成,由于MOS管的栅极和其它各极间有绝缘层相隔,在直流状态下,栅极无电流,所以静态时栅极不取电流,输入电平与外接电阻无关。由于MOS管在电路中是一压控元件,基于这一特点,输入端信号易受外界干扰,所以在使用CMOS门电路时输入端特别注意不能悬空。在使用时应采用以下方法:

1、与门和与非门电路:由于与门电路的逻辑功能是输入信号只要有低电平,输出信号就为低电平,只有全部为高电平时,输出端才为高电平。而与非门电路的逻辑功能是输入信号只要有低电平

- 关键字:

CMOS TTL

- 简介:本文总结了TTL和CMOS电平的特点、使用方式等内容 。

1,TTL电平(什么是TTL电平):

输出高电平>2.4V,输出低电平<0.4V。在室温下,一般输出高电平是3.5V,输出低电平是0.2V。最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V,噪声容限是0.4V。

特点:

1.CMOS是场效应管构成,TTL为双极晶体管构成

2.COMS的逻辑电平范围比较大(5~15V),TTL只能在5V下工作

3.CMOS的高

- 关键字:

TTL CMOS

- 我的显示屏是1024x768像素的TFT-LCD显示屏,LVDS输入,3路差分数据,1路差分时钟。

LCD是RGB565模式。kernel之前已经能够驱动一个7寸的屏幕工作,所以显示部分的修改不是很多。

修改源程序,增加对使用的LCD的支持。

修改/arch/arm/mach-omap2/board-am335xevm.c和/drivers/video/da8xx-fb.c,增加对LCD的支持,主要是修改几个数据结构。修改board-am335xevm.c的disp_panel,lc

- 关键字:

LCD LVDS

- “TTL电平”最常用于有关电专业,如:电路、数字电路、微机原理与接口技术、单片机等课程中都有所涉及。在数字电路中只有两种电平(高和低)高电平+5V、低电平0V.同样运用比较广泛的还有CMOS电平、232电平、485电平等。

TTL电路

TTL集成电路的主要型式为晶体管-晶体管逻辑门(transistor-transistor logic gate),TTL大部分都采用5V电源。

1.输出高电平Uoh和输出低电平Uol

Uoh≥2.4V,Uol&le

- 关键字:

TTL CMOS

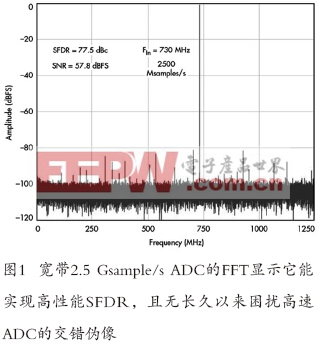

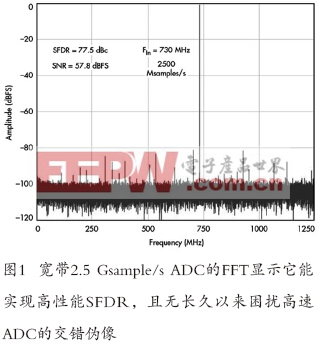

- 随着模数转换器(ADC)的设计与架构继续采用尺寸更小的过程节点,一种新的千兆赫ADC产品应运而生。能以千兆赫速率或更高速率进行直接RF采样且不产生交织伪像的ADC为通信系统、仪器仪表和雷达应用的直接RF数字化带来了全新的系统解决方案。

最先进的宽带ADC技术可以实现直接RF采样。就在不久前,唯一可运行在GSPS (Gsample/s)下的单芯片ADC架构是分辨率为6位或8位的Flash转换器。这些器件能耗极高,且通常无法提供超过7位的有效位数(ENOB),这是由于Flash架构的几何尺寸与功耗限

- 关键字:

ADC RF 转换器 LVDS FPGA

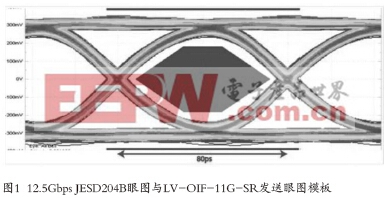

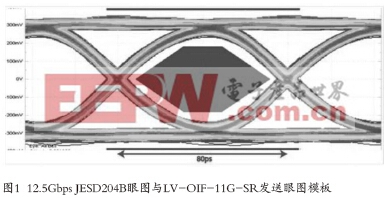

- 1 为不同应用提供不同选择

对于数据转换器的高速串行传输,不同的应用有不同的选择。十多年来,数据转换器制造商一直选择LVDS作为主要差分信号技术。尽管有些LVDS应用可使用更高的数据速率,但目前该市场上的转换器厂商可提供的最大LVDS数据速率仍然为0.8至1 Gbps。LVDS技术一直难以满足转换器的带宽要求。LVDS受TIA/EIA 644A规范控制,这是一项LVDS核心制造商的行业标准。该规范可作为设计人员的最佳实践指南,提高不同厂商的LVDS发送器及接收器兼容性。同样,没有完全遵守LVDS

- 关键字:

JESD204B LVDS 转换器 FPGA PHY

- 设计和制造硅基定时器件和频率控制产品的全球创新领导厂商ECS Inc. International欣然宣布2015年庆祝企业运营35周年。

ECS Inc.主席兼首席执行官Brad Slatten表示:“回顾以往成就,我们感到十分自豪。ECS公司拥有朝气蓬勃的团队合作、持续不断的产品开发,与客户合作并在最短时间内为其提供合适定时解决方案的决心,所有这些努力均已带来了回报,使得ECS公司成功地在这个竞争极为激烈的行业中立足35年。”

ECS Inc.的35年周年庆典恰

- 关键字:

ECS LVDS

lvds&ttl介绍

您好,目前还没有人创建词条lvds&ttl!

欢迎您创建该词条,阐述对lvds&ttl的理解,并与今后在此搜索lvds&ttl的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473