- 给出了DPLL的基本概念,阐述了DPLL的缺点,并结合最新的模拟锁相和数字锁相技术,提出了一种基于FPGA的全新锁相倍频系统的设计方法,简单地介绍了设计的思路、原理及其算法,并对该方案的性能进行了分析,给出了仿真波形。

- 关键字:

DPLL 锁相倍频系统 模拟锁相 数字锁相

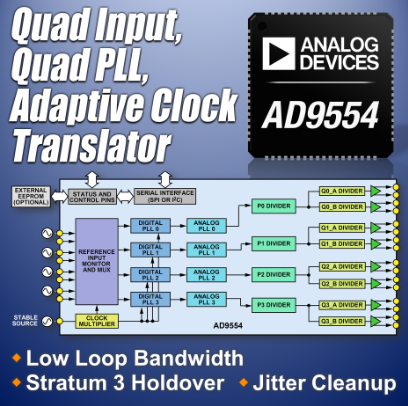

- Analog Devices, Inc.(NASDAQ:ADI)全球领先的高性能信号处理解决方案供应商,近日推出搭载时钟乘法器的多重服务型自适应四通道时钟转换器AD9554,该器件可以为多种系统提供抖动清除和同步功能,包括同步光纤网络(SONET/SDH)。与维持多个器件不同的时钟配置相比,其输入端嵌入的交叉点开关带来了更大的灵活性,降低了拥有成本。AD9554功耗仅为940 mW,同时还能在430 kHz至941 MHz的输出范围内产生最多8个输出时钟,与4个2 kHz至1 GHz外部输入参考时钟同

- 关键字:

ADI AD9554 DPLL

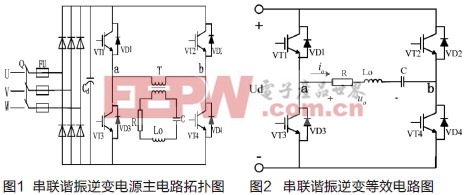

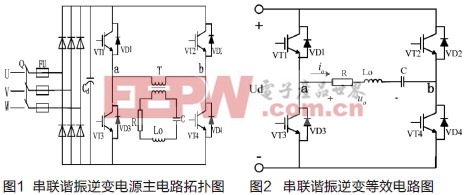

- 摘要:应用数字处理技术,研究了基于DSP的数字化控制的中频逆变电源。给出了基于IGBT的主电路拓扑结构,分析了其控制原理,采用基于TMS320F2407型DSP为核心的控制系统,实现串联谐振中频逆变电源的数字化控制,以满足系统控制的实时性和灵活性要求。研制了一台10kW/10kHz的逆变电源样机进行实验,实验结果验证了设计的有效性和可行性。

- 关键字:

逆变电源 DSP IGBT 串联谐振 DPLL 201310

- 摘要:针对跳频通信系统有固有噪声的特点,结合DDS+DPLL高分辨率、高频率捷变速度的优点,并采用Altera公司的Quartus-Ⅱ_10.1软件进行设计综合,提出了一种新型的跳频信号源。结果表明,该设计中DPLL时钟可达到12

- 关键字:

FPGA DPLL DDS 跳频信号源

- 在数字通信系统中,同步技术是非常重要的,而位同步是最基本的同步。位同步时钟信号不仅用于监测输入码元信号,确保收发同步,而且在获取帧同步及对接收的数字码元进行各种处理的过程中也为系统提供了一个基准

- 关键字:

FPGA DPLL 位同步时钟

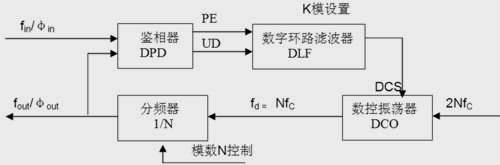

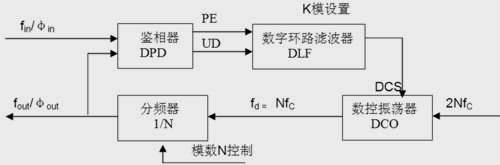

- 本文简要介绍了在FPGA中实现全数字锁相环(DPLL)的原理与方法,以解决在同步串行数据通信时的同步时钟不稳定时的快速恢复问题; 并重点介绍了采用可控模数分频器实现的数字锁相环中宽频带捕获的方法与实现过程。

- 关键字:

DPLL FPGA 数字环路滤波器 时钟恢复 宽频带

- 摘要: 本文简要介绍了在FPGA中实现全数字锁相环(DPLL)的原理与方法,以解决在同步串行数据通信时的同步时钟不稳定时的快速恢复问题; 并重点介绍了采用可控模数分频器实现的数字锁相环中宽频带捕获的方法与实现过程。关键词: DPLL;FPGA;数字环路滤波器;时钟恢复;宽频带

引言数字锁相环(DPLL)技术在数字通信、无线电电子学等众多领域得到了极为广泛的应用。与传统的模拟电路实现的PLL相比,DPLL具有精度高、不受温度和电压影响、环路带宽和中心频率编程可调、易于构建高阶锁相环等优

- 关键字:

DPLL 单片机 宽频带 嵌入式系统 数字锁相环

- 摘 要:本文提出了一种利用边沿触发鉴相缩短锁相环捕获时间的方案,并详细介绍了该方案基于FPGA的实现方法。通过对所设计的锁相环进行计算机仿真和硬件测试,表明该方案确实可以提高锁相环的捕获性能。关键词:数字锁相环(DPLL);捕获时间;FPGA;VHDL引言捕获时间是锁相环的一个重要参数,指的是锁相环从起始状态到达锁定状态所需时间。在一些系统中,如跳频通信系统,由于系统工作频率不断地发生快速变化(每秒几百次到几千次,甚至高达上万次),要求锁相环能够对信号相位快速捕获。因此

- 关键字:

FPGA VHDL 捕获时间 数字锁相环(DPLL)

- 摘要:本文在说明全数字锁相环的基础上,提出了一种利用FPGA设计一阶全数字锁相环的方法,并给出了关键部件的RTL可综合代码,并结合本设计的一些仿真波形详细描述了数字锁相环的工作过程,最后对一些有关的问题进行了讨论。关键词:全数字锁相环;DPLL;FSK;FPGA 引言锁相环(PLL)技术在众多领域得到了广泛的应用。如信号处理,调制解调,时钟同步,倍频,频率综合等都应用到了锁相环技术。传统的锁相环由模拟电路实现,而全数字锁相环(DPLL)与传统的模拟电路实现的PLL相比,具有精度高且不受温度和电压影响,环路

- 关键字:

DPLL FPGA FSK 全数字锁相环

dpll介绍

背景知识:

随着数字电路技术的发展,数字锁相环在调制解调、频率合成、FM 立体声解码、彩色副载波同步、图象处理等各个方面得到了广泛的应用。数字锁相环不仅吸收了数字电路可靠性高、体积小、价格低等优点,还解决了模拟锁相环的直流零点漂移、器件饱和及易受电源和环境温度变化等缺点,此外还具有对离散样值的实时处理能力,已成为锁相技术发展的方向。锁相环是一个相位反馈控制系统,在数字锁相环中,由于误差控制信号 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473