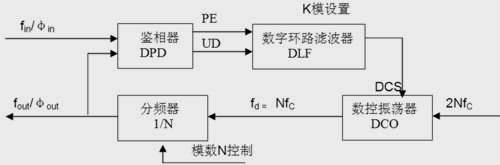

- 本文简要介绍了在FPGA中实现全数字锁相环(DPLL)的原理与方法,以解决在同步串行数据通信时的同步时钟不稳定时的快速恢复问题; 并重点介绍了采用可控模数分频器实现的数字锁相环中宽频带捕获的方法与实现过程。

- 关键字:

DPLL FPGA 数字环路滤波器 时钟恢复 宽频带

数字环路滤波器介绍

环路滤波器的性能优劣会直接影响到跟踪环路的性能。而采用数字化的环路滤波器便于调试参数和提高系统可靠性。环路滤波器的输出要直接控制频率合成器产生相应频率,使本地伪码能够准确跟踪发端信息。

基本原理:

数字环中使用的数字环路滤波器与模拟环中使用的环路滤波器作用一样,都对噪声及高频分量起抑制作用,并且控制着环路相位校正的速度与精度。适当选择滤波器的参数,可以改善环路的性能。数字环路滤波器的设计原 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473