- 摘要:叙述了全数字锁相环的工作原理,提出了应用VHDL 技术设计全数字锁相环的方法,并用复杂可编程逻辑器件CPLD 予以实现,给出了系统主要模块的设计过程和仿真结果。0 引言全数字锁相环(DPLL) 由于避免了模拟锁相环存

- 关键字:

VHDL 全数字 电路设计 锁相环

- 该应用笔记讨论了鉴频鉴相器的指标对锁相环(PLL)死区及抖动性能的影响。在使用电荷泵环路滤波的PLL设计中,通过产生具有最小脉宽的鉴相输出脉冲,可以减轻PLL的死区效应和相关的锁相环抖动。 锁相环广泛用于电信行业

- 关键字:

9382 MAX 锁相环 中的应用

- 0 引 言

电荷泵锁相环是闭环系统,系统各个部分都是一个噪声源,各部分噪声的大小不仅与电路本身有关,而且还与环路带宽等因素有关。因此,设计时必须分析其各频率范围内噪声源影响力的大小,权衡确定环路带宽与

- 关键字:

锁相环 环路带宽 分析 相位噪声

- 1.系统组成

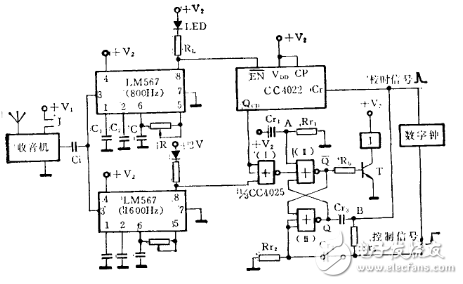

语音/文字短信无线发射机的系统方框图如图1所示,由集成电路MC1648、MC145152、MC12022、低通滤波器和晶振构成锁相环频率合成器、音频处理器、数据编码器、AT89S52单片机、按键、128×64点阵型LCD等部分

- 关键字:

发射机 设计 无线 短信 文字 语音 无线电发射机 锁相环 编码器 单片机

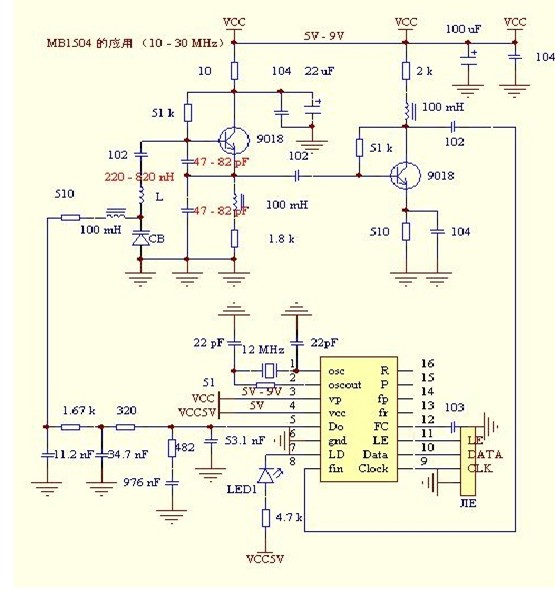

- 本文用锁相环频率合成器专用芯片MC145152及其外围电路设计了909~915 MHz步进25 kHz的频率合成器,该频率合成器具有较低的相位噪声、很高的频率稳定度,大大促进了数字锁相频率合成器集成化程度的提高和体积的缩小,满足了通信设备的高集成度和超小型化的要求,特别适合某些特殊场合的应用。

- 关键字:

锁相环 频率合成器 方案

- 1 引 言 锁相环是一种能使输出信号在频率和相位上与输入信号同步的电路,即系统进入锁定状态(或同步状态)后,震荡器的输出信号与系统输入信号之间相差为零,或者保持为常数。传统的锁相环各个部件都是由模拟电

- 关键字:

全数字 分析 锁相环

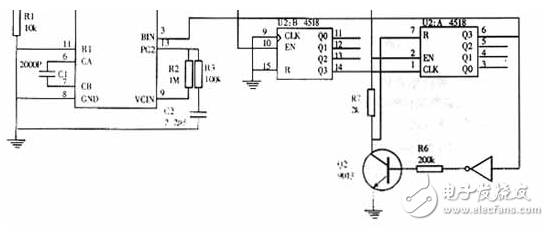

- 简单介绍了全数字锁相环(ADPLL)的结构和工作原理,提出一种在FPGA的基础上可增大全数字锁相环同步范围的设计方法,并给出了部分verilog HDL设计程序的代码和仿真波形。

- 关键字:

FPGA 全数字 锁相环

- 摘要: 介绍了一种超宽带雷达信号波形产生器的设计与实现,信号由DDS+PLL+混频器产生。该产生器采用高性能数字锁相环芯片Q3236、压控振荡器Q3500-0916T和混频器IAM-81008构成核心单元,利用新型低频和超带宽带通滤波器完成超宽带雷达信号。这种超宽带雷达信号的实现对提高现有雷达的性能以及研制新一代高性能雷达都具有重要意义。

关键词: 超宽带 直接数字合成 锁相环 混频器 滤波器

雷达是对远距离目标进行无线电探测、定位、测轨和识别的电子设备,无论对军用还是对民用,都占据重要位

- 关键字:

超宽带 直接数字合成 锁相环 混频器 滤波器

- Maxim推出基于晶体的锁相环(PLL) VHF/UHF发送器MAX7057,能够在较宽的频率范围内发送OOK/ASK/FSK数据。器件配合适当的晶体频率,可以发送300MHz至450MHz范围内的任何信号,并能够以高达100kbps的速率发送NRZ码(50kbps曼彻斯特码)。

MAX7057集成了可编程分数N PLL合成器和宽带VCO,因而具有极大的灵活性。此外,还可以设置内部电容,实现功率放大器(PA)与天线之间的阻抗匹配。这种拓扑结构可确保多个工作频率下的高效率传输,从而使MAX7057

- 关键字:

Maxim PLL 锁相环 发送器

- 近年来诞生了许多种类的脉宽调整电路。这些电路大致可以分为以下三类:第一类最为简单,即采用2分频器产生占空比为50%的时钟,2分频器并不是专为调整占空比而采用的,但的确达到了这一需求;第二类通过负反馈机制,采用数字或模拟控制,调整信号占空比,这类电路最主要考虑的是系统稳定性;最后一种是采用复杂数字算法的占空比调整电路,其实现相对比较复杂。因此本文主要分析设计前两种类型的脉宽调整电路。

- 关键字:

应用于 锁相环 脉宽 调整电路

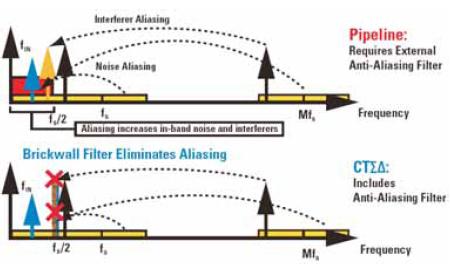

- 连续时间SD调制器

第一枚获业界公认的SD调制器诞生于1962年,而它事实上是采用了CT电路。此后,利用CT电路来实现SD调制器便愈来愈普遍,但当开关电容器(SC)电路面世后,大部分的SD调制器都改以DT环路滤波器来实现。SC电路之所以受欢迎,原因是它不会受信号波形特性的影响。此外,SC积分器的时间常数可随着采样频率而调整,从而提高系统的灵活性。可是,其后CTΣΔ调制器又因其某些优点而重新受到注视,例如是它采用较低功耗的积分放大器,以及内置有采样输入模/数转换器没有的抗混叠滤

- 关键字:

转换器 CTΣΔ调制器 锁相环 采样时钟 NI 200806

- Maxim推出基于晶体的锁相环(PLL) VHF/UHF发送器MAX7058,能够在315MHz或390MHz下发送OOK/ASK/FSK数据。该器件采用单个15MHz晶体,能够支持315MHz/390MHz之间的切换工作,采用不同频率的晶体可以使器件工作在300MHz至450MHz范围内的任意2个频率下。MAX7058集成了具有内部调谐电容的多频率VCO,可将功率放大器(PA)的阻抗设置到与天线相匹配的值,从而提高了灵活性。该架构保证了多个工作频率下的高效传输,因而使MAX7058成为家庭安全系统、

- 关键字:

Maxim 锁相环 VHF/UHF 发送器

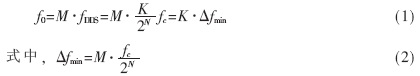

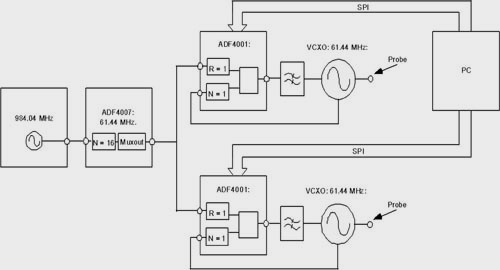

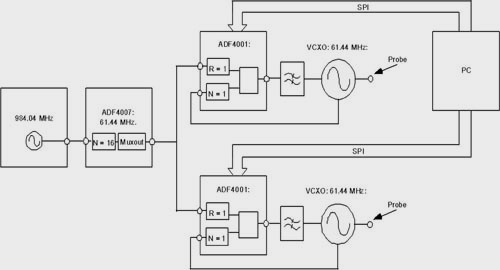

- 锁相环(PLL)广泛应用于无线通信,在基站中的主要用途是为发射器和接收器中的上变频和下变频电路提供一个稳定的、低噪声的射频(RF)本地振荡器(LO)。鉴于PLL本身的性能,它还可以用于控制其他许多电路中时钟信号的定时,而且在某些应用中,如果使用得当可以代替价格较贵的定时芯片。

大多数高速数字电路的设计工程师会在注重相位的应用中选择很贵的定时芯片,因为通常都是对限定频率范围(通常是适合SONET/SDH频率的线路速率)粗略地表征定时指标。相比之下,PLL器件通常覆盖了很宽的频率范围,而且在相位控制

- 关键字:

锁相环 PLL

锁相环介绍

能使受控振荡器的频率和相位均与输入信号保持确定关系的闭环电子电路。锁相环的基本结构如图1,其中鉴相器用来鉴别输入信号ui与输出信号u0之间的相位差,并输出误差电压ud。ud中的噪声和干扰成分被低通性质的环路滤波器滤除,形成压控振荡器(VCO)的控制电压uC。uC作用于压控振荡器的结果是把它的输出振荡频率f0拉向环路输入信号频率fi,当二者相等时,环路被锁定,称为入锁。维持锁定的直流控制电压由鉴相器 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473