- 多加数的加法器是FPGA的一个比较常见的应用。仿真对比了其三种实现方案的性能和所消耗资源,得出进位保留加法阵列是首选方案。针对进位保留加法阵列实现的复杂性给出了一个加法阵列的HDL代码生成器,极大地简化了加法阵列的设计工作。

- 关键字:

HDL代码生成器 加法器 FPGA

- 加法器 :

加法器是为了实现加法的。

即是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

对于1位的二进制加法,相关的有五个的量:1,被加数A,2,被加数B,3,前一位的进位CIN,4,此位二数相加的和S,5,此位二数相加产生的进位COUT。前三个量为输入量,后两个量为输出量,五个量均为1位。

对于32位的二进制加法,相关的也有五个量

- 关键字:

加法器

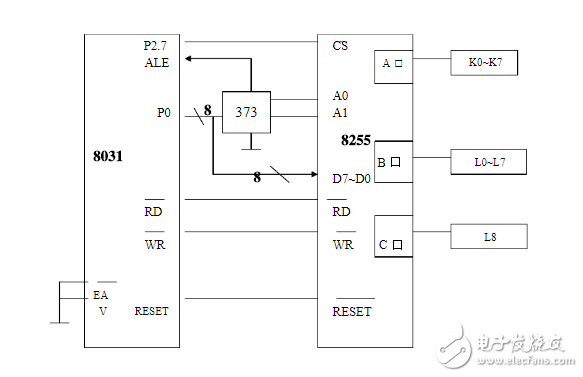

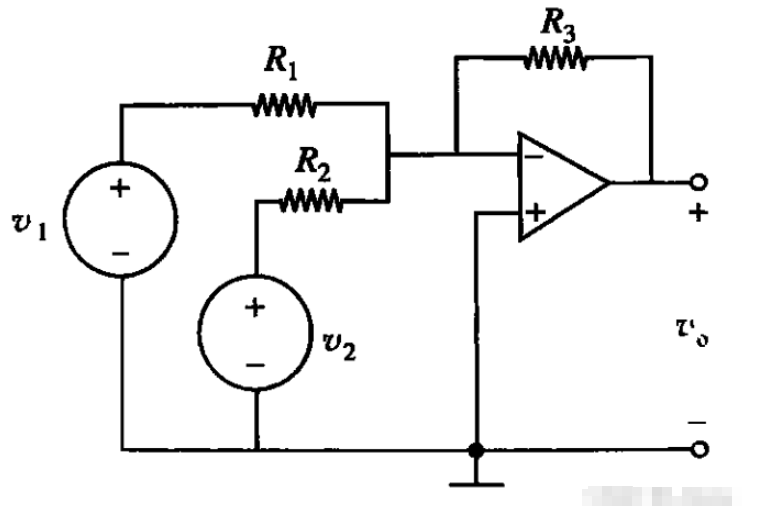

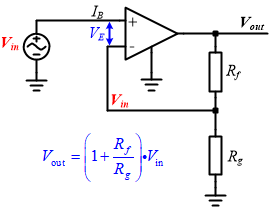

- 随着FPGA的功能日益强大和完善,FPGA在项目中的应用也越来越广泛,其技术关键在于控制日益广泛而丰富的外围器件。本文以Flash存储器件为FPGA的外围,叙述了FPGA中SPI总线接口的Flash驱动模块的设计,其接口基本符合Avalon总线的规范要求,并且通过实际的读写操作验证。传统反相运算放大器的加法器配置利用反相输入端的低阻抗节点(虚拟地)的特性而实现。加法电路非常直观且易于分析和使用,不过它确实存在某些限制。面对常规或复杂电路功能时,运算放大器非常好用,可提供很多实用且

- 关键字:

DAI 加法器 放大器 电路

- 摘要:浮点运算器的核心运算部件是浮点加法器,它是实现浮点指令各种运算的基础,其设计优化对于提高浮点运算的速度和精度相当关键。文章从浮点加法器算法和电路实现的角度给出设计方法,通过VHDL语言在OuartusII中进

- 关键字:

FPU 加法器

- 随着仪表放大器价格的逐步下滑,它们可以为传统上采用运算放大器的应用提供更高的性能。图1中的运放加法器有一些缺点。首先,输入端为中低输入阻抗,这是由每个信号的输入电阻所决定的。当驱动信号源阻抗较大,或需要

- 关键字:

仪表放大器 性能 加法器

- 本工程设计完全符合IP核设计的规范流程,而且完成了Verilog HDL建模、功能仿真、综合、时序仿真等IP核设计的整个过程,电路功能正确。实际上,本系统在布局布线后,其系统的最高时钟频率可达80MHz。虽然使用浮点数会导致舍入误差,但这种误差很小,可以忽略。实践证明,本工程利用流水线结构,方便地实现了高速、连续、大数据量浮点数的加法运算,而且设计结构合理,性能优异,可以应用在高速信号处理系统中。

- 关键字:

FPGA 流水线 浮点 加法器

- 摘 要:在FPGA上实现单精度浮点加法器的设计,通过分析实数的IEEE 754表示形式和IEEE 754单精度浮点的存储格式,设计出一种适合在FPGA上实现单精度浮点加法运算的算法处理流程,依据此算法处理流程划分的各个处理模块

- 关键字:

FPGA 精度 浮点 加法器

- 在数字电路中,常需要进行加、减、乘、除等算术运算,而乘、除和减法运算均可变换为加法运算,故加法运算电路应用十分广泛。

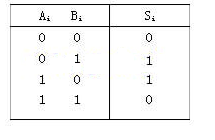

1.半加器

不考虑由低位来的进位,只有本位两个数相加,称为半加器。图1(a)为半加器的方框图。其中:A、B分别为被加数与加数,作为电路的输入端;S为两数相加产生的本位和,它和两数相加产生的向高位的进位C一起作为电路的输出。

图1 半加器框图、逻辑图和符号

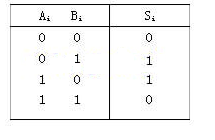

根据二进制数相加的原则,得到半加器的真值表如表1所列。

表1 半加器的真值表

- 关键字:

加法器 逻辑电路

- 高速数字串行加法器及其应用 深圳南山区科技园中兴通讯IC开发一部(518057) 钟信潮上海盛立亚光网络系统有限公司 薛小刚深圳南山区科技园中兴通讯3G开发(518057) 王 诚

摘 要:与传统加法器相比,数字串行加法器具有工作频率高、占用资源少、设计灵活等优点。介绍了数字串行加法器的原理,说明了该加法器在FPGA上的实现要点及其在匹配滤波器设计中的应用。 关键词:加法器 位并行 数字串行 FPGA 匹配滤波器

与传统DSP相比,定制DSP具有速度更高、设计灵活、易于更改

- 关键字:

FPGA 加法器 匹配滤波器 数字串行 位并行

加法器介绍

目录

1 简介

2 基本方法

3 工作原理

4 类型

5 结构设计

6 逻辑优化

简介

加法器是为了实现加法的。

即是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

对于1位的二进制加法,相 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473